CECS 341 Quiz 4

1/49

There's no tags or description

Looks like no tags are added yet.

Name | Mastery | Learn | Test | Matching | Spaced |

|---|

No study sessions yet.

50 Terms

Which if the following have fewer transistors per bit in memory?

a. DRAM

b. SRAM

a. DRAM

In a directed map cache with 8 1-word blocks and given block address 1 9 6 5 1 6, the 1st block 1 is a ___.

a. hit

b. miss

b. miss

In a directed map cache with 8 1-word blocks and given block address 1 9 6 5 1 6, the 2nd block 9 is a ___.

a. hit

b. miss

b. miss

In a directed map cache with 8 1-word blocks and given block address 1 9 6 5 1 6, the 3rd block 6 is a ___.

a. hit

b. miss

b. miss

In a directed map cache with 8 1-word blocks and given block address 1 9 6 5 1 6, the 4th block 5 is a ___.

a. hit

b. miss

b. miss

In a directed map cache with 8 1-word blocks and given block address 1 9 6 5 1 6, the 5th block 1 is a ___.

a. hit

b. miss

b. miss

In a directed map cache with 8 1-word blocks and given block address 1 9 6 5 1 6, the 6th block 6 is a ___.

a. hit

b. miss

a. hit

In a 2-way set associative cache with 8 1-word blocks and given block address 1 9 6 5 1 6, the 1st block 1 is a ___.

a. hit

b. miss

b. miss

In a 2-way set associative cache with 8 1-word blocks and given block address 1 9 6 5 1 6, the 4th block 5 is a ___.

a. hit

b. miss

b. miss

In a 2-way set associative cache with 8 1-word blocks and given block address 1 9 6 5 1 6, the 5th block 1 is a ___.

a. hit

b. miss

b. miss

In a fully associative cache with 8 1-word blocks and given block address 1 9 6 5 1 6, the 6th block 6 is a ___.

a. hit

b. miss

a. hit

Assume the miss rate of an instruction cache is 2% and the miss rate of the data cache is 4%. If a processor has a CPI of 2 without any memory stalls, and the miss penalty is 100 cycles for all misses, what is the total CPI? Assume the frequency of all loads and stores is 36%.

The total CPI is _____.

a. 1.44

b. 3.44

c. 5.44

c. 5.44

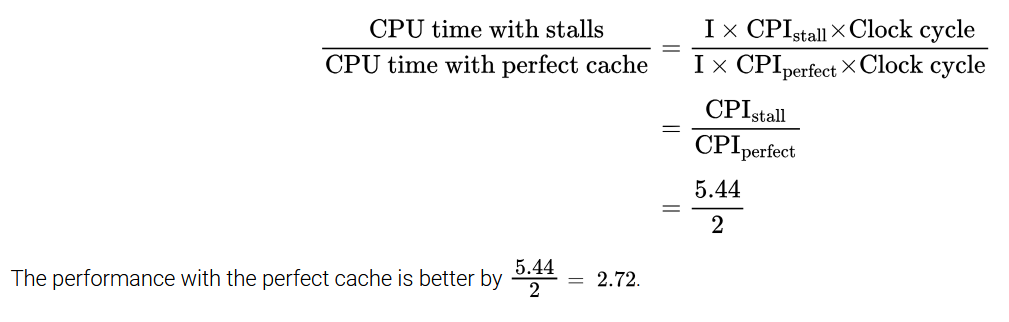

Assume the miss rate of an instruction cache is 2% and the miss rate of the data cache is 4%. If a processor has a CPI of 2 without any memory stalls, and the miss penalty is 100 cycles for all misses, determine how much faster a processor would run with a perfect cache that never missed. Assume the frequency of all loads and stores is 36%.

The number of memory-stall cycles for data misses in terms of the instruction count (I) is _____.

a. I × 4% × 100

b. I × 36% × 4%

c. I × 36% × 4% × 100

c. I × 36% × 4% × 100

Assume the miss rate of an instruction cache is 2% and the miss rate of the data cache is 4%. If a processor has a CPI of 2 without any memory stalls, and the miss penalty is 100 cycles for all misses, determine how much faster a processor would run with a perfect cache that never missed. Assume the frequency of all loads and stores is 36%.

The performance with the perfect caches is faster by ____.

a. 2.72

b. 1.72

c. 1

a. 2.72

Suppose that in 1000 memory references there are 40 misses in the first-level cache and 20 misses in the second-level cache. Assume the miss penalty from the L2 cache to memory is 200 clock cycles, the hit time of the L2 cache is 10 clock cycles, the hit time of the L1 is 1 clock cycle, and there are 1.5 memory references per instruction. Ignore the impact of writes.

What is the local miss rate of L1?

a. 50%

b. 4%

c. 2%

b. 4%

Suppose that in 1000 memory references there are 40 misses in the first-level cache and 20 misses in the second-level cache. Assume the miss penalty from the L2 cache to memory is 200 clock cycles, the hit time of the L2 cache is 10 clock cycles, the hit time of the L1 is 1 clock cycle, and there are 1.5 memory references per instruction. Ignore the impact of writes.

What is the global miss rate of L1?

a. 50%

b. 4%

c. 2%

b. 4%

Suppose that in 1000 memory references there are 40 misses in the first-level cache and 20 misses in the second-level cache. Assume the miss penalty from the L2 cache to memory is 200 clock cycles, the hit time of the L2 cache is 10 clock cycles, the hit time of the L1 is 1 clock cycle, and there are 1.5 memory references per instruction. Ignore the impact of writes.

What is the global miss rate of L2?

a. 50%

b. 4%

c. 2%

c. 2%

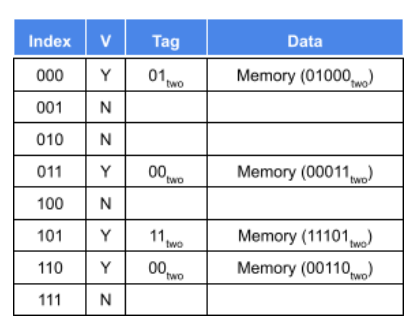

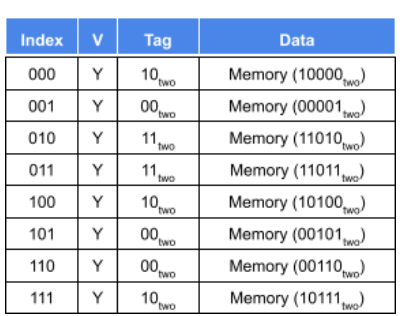

After a request to address 00101two, the data in cache block 101two is

a. 11101

b. 00101

b. 00101

After a request to address 10000two, the data in cache block 000two is

a. empty

b. not changed

b. not changed

Memories in personal mobile devices are typically _____.

a. flash memory

b. magnetic disk

a. flash memory

If an instruction access results in a miss, then the address of the instruction at _____ is fetched from the memory.

a. PC

b. PC - 4

c. PC + 4

b. PC - 4

The minimum unit of information that can be either present or not present in the memory hierarchy is a _____.

a. bit

b. block

b. block

Instructions may exhibit temporal locality, but never spatial locality.

a. True

b. False

b. False

A four-way set-associative cache with 32-one word blocks requires _____ comparators to compare the tags of each element within the set.

a. 2

b. 4

c. 8

d. 16

e. 32

b. 4

A direct mapped cache with 32-one word blocks requires _____ comparator(s) to compare the tags of of an element with the memory block address.

a. 1

b. 32

a. 1

Which block in the cache is replaced by memory block 29?

Cache configuration: 4-way set-associative cache with 8-one word blocks

Replacement scheme: LRU

Sequence of previously accessed block addresses: 5, 13, 21, 13, 5

(Note: All memory block addresses map to cache set 1)

a. Mem[5]

b. Mem[13]

c. Mem[21]

d. None. An element in set 1 is unused, so Mem[29] is placed in the fourth element of set 1.

d. None. An element in set 1 is unused, so Mem[29] is placed in the fourth element of set 1.

A VMM should not allow a guest VM to change how resources are allocated.

a. True

b. False

a. True

A VMM runs in system mode, while a guest VM runs in user mode.

a. True

b. False

a. True

Physical pages can be shared by having two virtual addresses point to the same physical address.

a. True

b. False

a. True

The page offset of a virtual page is directly copied to the page offset field of a physical page if requested and present in memory.

a. True

b. False

a. True

On a read miss, check the contents of the write buffer and if there are no conflicts and the memory system is available, let the read miss continue to reduce miss penalty.

a. True

b. False

a. True

A one value in the reference field of a TLB indicates a miss.

a. True

b. False

b. False

A zero value in the dirty field of TLB shows a write operation.

a. True

b. False

b. False

Write-back only updates the block in the cache.

a. True

b. False

a. True

Block access sequence 0, 8, 0, 6, and 8 are used to compare three different caches such as direct mapped, 2-way associative, and fully associative assuming each cache consisting of four one-word block (LCU is used for the replacement policy). Which cache will exhibit the lowest miss rate?

a) direct-mapped

b) 2-way associative

c) fully associative

c. Fully associative

Assume a direct-mapped cache with 32 blocks and a block size of 8 bytes.

Byte address 400 maps to block number _____.

a. 13

b. 18

c. 32

d. 45

e. 50

b. 18

The number of virtual pages should be equal to the number of physical pages.

a. True

b. False

b. False

The following sequence of nine memory references in word address (22, 26, 22, 26, 16, 3, 16, 18, and 12) is directly mapped to an empty eight-block cache with one word per block. What is the hit rate?

a) 4/9

b) 5/9

c) 6/9

d) 7/9

e) None of the above

e. None of the above

Assume a direct-mapped cache with 32 blocks and a block size of 8 bytes.

Byte address 360 maps to block number _____.

a. 13

b. 32

c. 45

d. 50

a. 13

Assume a direct-mapped cache with 32 blocks and a block size of 8 bytes.

Byte address 360 maps to block address _____.

a. 13

b. 32

c. 45

d. 50

c. 45

2:1 cache rule of thumb states a direct-mapped cache of size N has about the same miss rate as a two-way set-associative cache of size N/2.

a. True

b. False

a. True

In a page table, a physical address is located by indexing a virtual page number.

a. True

b. False

a. True

The virtual address indicates the location of the page table in memory.

a. True

b. False

b. False

Data may exhibit spatial locality, but never temporal locality.

a. True

b. False

b. False

The first access to a block cannot be in the cache, so the block must be brought into the caches. Also called cold-start misses or first-reference misses.

a. Compulsory

b. Capacity

d. Conflict

a. Compulsory

A directed map with cache size 64 k bytes, 128 bits per block, and 32 bit memory address has a word offset size of ____.

a. 0

b. 2

c. 4

b. 2

A directed map with cache size 64 k bytes, 128 bits per block, and 32 bit memory address has an index size ____.

a. 0

b. 8

c. 10

d. 12

d. 12

For a two-level cache, the first-level can be ___ enough to match the processor and the second level large enough to capture many accesses that would go to main memory which would lessen the miss penalty.

a. slow

b. fast

b. fast

RAM can both read and write.

a. True

b. False

a. True

Block access sequence 0, 8, 0, 6, and 8 are used to compare three different caches such as direct mapped, 2-way associative, and

fully associative assuming each cache consisting of 16 one-word block (LCU is used for the replacement policy). Which cache will

exhibit the lowest miss rate?

a. Fully associative

b. Direct mapped

c. 2-way associative

d. All of them

d. All of them