cấu trúc máy tính

0.0(0)Studied by 0 people

Card Sorting

1/101

Earn XP

Description and Tags

Last updated 9:26 AM on 6/11/23

Name | Mastery | Learn | Test | Matching | Spaced | Call with Kai |

|---|

No analytics yet

Send a link to your students to track their progress

102 Terms

1

New cards

các thành phần cơ bản của máy tính

CPU

Bộ nhớ chính

Module I/O

System Bus

Bộ nhớ chính

Module I/O

System Bus

2

New cards

máy tính có bn thành phần cơ bản

4 thành phần cơ bản

3

New cards

Module I/O có công dụng

giúp CPU, bộ nhớ tiếp xúc với thiết bị ngoại vi

4

New cards

các thành phần trong CPU

Bộ điều khiển

ALU

thanh ghi (bộ nhớ tạm thời)

kết nối bên trong

ALU

thanh ghi (bộ nhớ tạm thời)

kết nối bên trong

5

New cards

Máy tính đầu tiên

ENIAC

// 1943-1946, hệ thập phân

// 1943-1946, hệ thập phân

6

New cards

có bn giai đoạn trong lịch sử máy tính

4 hoặc 6

7

New cards

các giai đoạn trong lịch sử máy tính

* bóng chân không

* bóng bán dẫn

* mạch tích hợp (vừa và nhỏ, lớn, rất lớn, siêu lớn)

* bóng bán dẫn

* mạch tích hợp (vừa và nhỏ, lớn, rất lớn, siêu lớn)

8

New cards

Kiến trúc Von Neumann

* nằm trong giai đoạn 1

* chương trình lưu trong bộ nhớ

* máy tính IAS

* 4 thành phần: MM, ALU (hệ 2) , CU, I/O

* chương trình lưu trong bộ nhớ

* máy tính IAS

* 4 thành phần: MM, ALU (hệ 2) , CU, I/O

9

New cards

giai đoạn 2 trong lịch sử máy tính

* sử dụng bóng bán dẫn

* nhỏ hơn, rẻ hơn, ít tản nhiệt hơn

* có ngôn ngữ chương trình bậc cao

* nhỏ hơn, rẻ hơn, ít tản nhiệt hơn

* có ngôn ngữ chương trình bậc cao

10

New cards

giai đoạn 3 trong lịch sử máy tính

* mạch tích hợp (tích hợp rất nhiều bóng bán dẫn trong 1 con chip)

* dựa vào số lượng bóng bán dẫn để chia mức độ, quy mô

* dựa vào số lượng bóng bán dẫn để chia mức độ, quy mô

11

New cards

Định luật Moore

* 1965

* số lượng transistors trên 1 con chip tăng gấp đôi mỗi 18 tháng

* số lượng transistors trên 1 con chip tăng gấp đôi mỗi 18 tháng

12

New cards

bộ nhớ bán dẫn

* tạo từ bóng bán dẫn

* 1970

* đọc k phá hủy

* dung lượng tăng, chạy nhanh

* thời đầu thì giá cao

* chip đơn lớn nhất hiện tại 1T

* 1970

* đọc k phá hủy

* dung lượng tăng, chạy nhanh

* thời đầu thì giá cao

* chip đơn lớn nhất hiện tại 1T

13

New cards

trong các họ vi xử lý thì

mọi thứ đều tăng, chỉ có kích thước của transistor thì được giảm

// clock speeds dậm chân, để tập trung phát triển về bộ nhớ

// clock speeds dậm chân, để tập trung phát triển về bộ nhớ

14

New cards

clock speed

xung nhiệt cao, tốc độ xử lý nhanh nhưng điện cao, giá cả cao

15

New cards

MIPS = (Số lệnh thực thi) / (Thời gian thực thi) \* 10^-6

MIPS = f/ (CPI \*10 mũ 6)

MIPS = f/ (CPI \*10 mũ 6)

công thức tính MIPS

16

New cards

chuyển đổi từ hệ 10 qua hệ x

chia lấy ngược tới khi thương =0, nhân lấy xuôi tới khi phần thập phân =0

17

New cards

từ hệ X qua hệ 10

ký tự \* trọng số + lại

18

New cards

khi chuyển từ hệ 2 qua hệ 8 hoặc hệ 16

* gom bit để chuyển

* phần nguyên thì gom từ phải

* phần thập phân thì gom từ trái

* phần nguyên thì gom từ phải

* phần thập phân thì gom từ trái

19

New cards

cộng trừ nhị phân

* 1+1=0 (nhớ 1)

* 0 - 1 =1 (mượn 1)

* 0 - 1 =1 (mượn 1)

20

New cards

số nhị phân có dấu - số bù hai

đảo bit cộng 1

21

New cards

số nhị phân có dấu n bit với phương pháp Dấu và độ lớn

* bit đầu thể hiện dấu, 1 là âm, 0 là dương

* n-1 bit còn lại thể hiện giá trị

* n-1 bit còn lại thể hiện giá trị

22

New cards

phạm vi biểu diễn của số nhị phân có dấu n bit

từ - 2 mũ (n-1) đến 2 mũ (n-1) -1 (số bù 2)

từ - 2 mũ (n-1) +1 đến 2 mũ (n-1) -1 (dấu và độ lớn)

từ - 2 mũ (n-1) +1 đến 2 mũ (n-1) -1 (dấu và độ lớn)

23

New cards

tìm giá trị của số âm (dãy bit có bit đầu là 1)

cách 1: khai triển bth, nhưng bit lớn nhất \*(-1)

cách 2: đảo bit+1 được số dương cùng biên độ

cách 2: đảo bit+1 được số dương cùng biên độ

24

New cards

cách mở rộng bit đối với số âm mà không thay đổi giá trị

thêm số 1 ở trước

25

New cards

đối với số không dấu

nếu có nhớ ra ngoài thì phép tính sai

26

New cards

đối với số có dấu

* nếu cộng hai số cùng dấu ra khác dấu thì phép tính sai

27

New cards

kí hiệu khoa học

N = ± M \* X mũ E

( 1

( 1

28

New cards

số dấu phẩy động kiểu đơn

* 32 bit

* 1 - 8 - 23 s - e - m dấu mũ định trị

* nếu m còn dư bit thì thêm 0 vào sau

* e =E+127

* m là phần thập phân của M

* công thức xác định giá trị số thực

X= (-1)^S \* 1.m \* 2^(e-127)

* 1 - 8 - 23 s - e - m dấu mũ định trị

* nếu m còn dư bit thì thêm 0 vào sau

* e =E+127

* m là phần thập phân của M

* công thức xác định giá trị số thực

X= (-1)^S \* 1.m \* 2^(e-127)

29

New cards

các tiên đề, định lý cơ bản trong đại số BOOLE

* x+(y.z)=(x+y).(x+z)

* x+1=1

* x. x bù =0

* x+x=x

* x\*x=x

* x+x.y=x

* x.(x+y)=x

* x + (bù x \*y)=x+y

* x nhân (bù x +y)=x nhân y

* x.y +bù x .z +y.z=x.y+bù x .z

* x+1=1

* x. x bù =0

* x+x=x

* x\*x=x

* x+x.y=x

* x.(x+y)=x

* x + (bù x \*y)=x+y

* x nhân (bù x +y)=x nhân y

* x.y +bù x .z +y.z=x.y+bù x .z

30

New cards

định lý de morgan

* bù tổng là tích

* bù tích là tổng

* bù tích là tổng

31

New cards

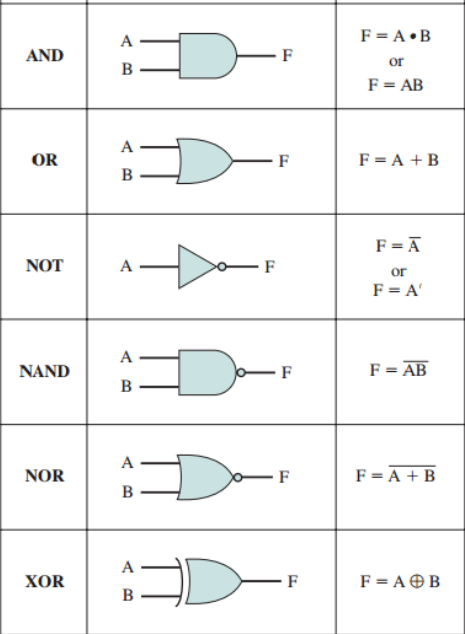

cổng logic

32

New cards

cổng NAND

* = 0 nếu mọi số =1

* =1 nếu tồn tại 1 số =0

* =1 nếu tồn tại 1 số =0

33

New cards

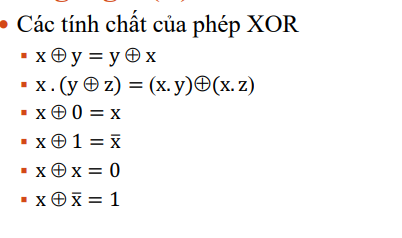

cổng XOR

= 1 nếu số đầu vào =1 lẻ

=0 nếu số đầu vào = 1 chẵn

=0 nếu số đầu vào = 1 chẵn

34

New cards

ghép cổng logic

* đối với cổng NAND,

1 NAND →NOT, 2 NAND →AND, 3 NAND→OR

* đối với cổng NOR

1 NOR → NOT, 2 NOR →OR, 3 NOR →AND

1 NAND →NOT, 2 NAND →AND, 3 NAND→OR

* đối với cổng NOR

1 NOR → NOT, 2 NOR →OR, 3 NOR →AND

35

New cards

bộ nhớ đánh địa chỉ theo từ

* từ dung lượng tìm số bit

lấy dung lượng bộ nhớ chia cho số bit 1 từ →số từ

→ số bit địa chỉ là số mũ của số từ

* từ số địa chỉ từ →dung lượng

2 mũ số địa chỉ từ ra số từ

số từ \*số bit mỗi từ →dung lượng

lấy dung lượng bộ nhớ chia cho số bit 1 từ →số từ

→ số bit địa chỉ là số mũ của số từ

* từ số địa chỉ từ →dung lượng

2 mũ số địa chỉ từ ra số từ

số từ \*số bit mỗi từ →dung lượng

36

New cards

bộ nhớ đánh địa chỉ theo byte

* từ dung lượng ra số địa chỉ từ

log2(dung lượng)

* từ số địa chỉ từ ra dung lượng

dung lượng = 2 mũ (số địa chỉ từ)

log2(dung lượng)

* từ số địa chỉ từ ra dung lượng

dung lượng = 2 mũ (số địa chỉ từ)

37

New cards

các thanh ghi trong CPU bao gồm

* thanh ghi đặc biệt (có giá trị sẵn)

PC: bộ đếm chương trình

IR

MAR

MBR

I/O AR

I/O BR

* thanh ghi chung (lưu giá trị tạm thời)

PC: bộ đếm chương trình

IR

MAR

MBR

I/O AR

I/O BR

* thanh ghi chung (lưu giá trị tạm thời)

38

New cards

chức năng cơ bản của máy tính:

thực hiện chương trình

39

New cards

4 loại câu lệnh

* đọc, ghi bộ nhớ

* nhập xuất dữ liệu

* xử lý dữ liệu

* điều khiển (nhảy, rẽ nhánh, kiểm tra)

* nhập xuất dữ liệu

* xử lý dữ liệu

* điều khiển (nhảy, rẽ nhánh, kiểm tra)

40

New cards

Giản đồ thời gian của một chu kỳ lệnh

b1: tính toán địa chỉ câu lệnh

b2: lấy lệnh

b3: giải mã lệnh

b4: tính toán địa chỉ toán hạng

b5: lấy toán hạng

b6: thực hiện phép toán

b7: tính toán địa chỉ toán hạng kết quả

b8: lưu kq

b9: ktr ngắt

b10: ngắt

b2: lấy lệnh

b3: giải mã lệnh

b4: tính toán địa chỉ toán hạng

b5: lấy toán hạng

b6: thực hiện phép toán

b7: tính toán địa chỉ toán hạng kết quả

b8: lưu kq

b9: ktr ngắt

b10: ngắt

41

New cards

ngắt

tạm dừng hoạt động CPU trong một thời gian ngắn để ngắt

42

New cards

các loại ngắt

* ngắt cứng (phần lớn) (do TBNV) (không báo trước)

* ngắt mềm (do chương trình) (không báo trước)

* ngắt khác (báo trước)

* ngắt mềm (do chương trình) (không báo trước)

* ngắt khác (báo trước)

43

New cards

mục đích của ngắt

tối ưu hóa việc sử dụng tài nguyên trong môi trường (CPU), tránh CPU nhàn rỗi khi các thiết bị I/O thực hiện

44

New cards

CPU kiểm tra có ngắt hay không khi nào?

CPU sẽ kiểm tra có ngắt hay không tại cuối chu kỳ thực hiện mỗi lệnh

45

New cards

Cơ chế ngắt (2)

* Ngắt tuần tự

* Ngắt ưu tiên

* Ngắt ưu tiên

46

New cards

bus interconnection

kết nối các thành phần trong máy tính

47

New cards

các loại bus interconnection

* đọc

* ghi

* nhập dl

* xuất dl

* I/O với bộ nhớ

* ghi

* nhập dl

* xuất dl

* I/O với bộ nhớ

48

New cards

bus structure

* bus dl: truyền dl →***quyết định tốc độ***

* bus địa chỉ: truyền địa chỉ →***dl bộ nhớ tối đa mà máy tính có thể truy cập***

* control lines

* bus địa chỉ: truyền địa chỉ →***dl bộ nhớ tối đa mà máy tính có thể truy cập***

* control lines

49

New cards

type bus

* dedicated: riêng biệt

* multiplexed: dùng chung

* multiplexed: dùng chung

50

New cards

method of arbitration

* centralized: tập trung (chỉ 1 bộ abiter)

* distributed: phân tán (mỗi thiết bị 1 abiter)

bus abiter: điều khiển, phân quyền sử dụng bus

* distributed: phân tán (mỗi thiết bị 1 abiter)

bus abiter: điều khiển, phân quyền sử dụng bus

51

New cards

các thành phần của lệnh máy

* Opcode (mã hoạt động) (luôn có)

* Địa chỉ toán hạng nguồn

* địa chỉ toán hạng đích

* địa chỉ của câu lệnh tiếp theo mà nó thực hiện (nằm trong nhóm lệnh control)

không phải câu lệnh nào cx chứa đủ

* Địa chỉ toán hạng nguồn

* địa chỉ toán hạng đích

* địa chỉ của câu lệnh tiếp theo mà nó thực hiện (nằm trong nhóm lệnh control)

không phải câu lệnh nào cx chứa đủ

52

New cards

toán hạng nguồn và toán hạng đích có thể nằm ở

* bộ nhớ

* I/O device

* thanh ghi

* immediate

* I/O device

* thanh ghi

* immediate

53

New cards

các nhóm lệnh

* xử lý dữ liệu (+-x:, and or xor not…)

* lưu trữ dữ liệu

* di chuyển dl (làm việc với I/O nhập xuất)

* điều khiển

* lưu trữ dữ liệu

* di chuyển dl (làm việc với I/O nhập xuất)

* điều khiển

54

New cards

ngôn ngữ assemble

là ngôn ngữ bậc thấp, quan hệ 1:1 với mã máy

55

New cards

move A,B

A=B

56

New cards

mode địa chỉ (7)

* immediate (0 truy cập bộ nhớ, 0 truy cập thanh ghi)

* direct (1 truy cập bộ nhớ, 0 truy cập thanh ghi)

* indirect (2 truy cập bộ nhớ, 0 truy cập thanh ghi)

* mode thanh ghi (0 truy cập bộ nhớ, 1 truy cập thanh ghi)

* mode thanh ghi gián tiếp (1 truy cập bộ nhớ, 1 truy cập thanh ghi)

* displacement (hằng số + nội dung thanh ghi) (1 truy cập bộ nhớ)

* implicit (0 truy cập bộ nhớ)

* direct (1 truy cập bộ nhớ, 0 truy cập thanh ghi)

* indirect (2 truy cập bộ nhớ, 0 truy cập thanh ghi)

* mode thanh ghi (0 truy cập bộ nhớ, 1 truy cập thanh ghi)

* mode thanh ghi gián tiếp (1 truy cập bộ nhớ, 1 truy cập thanh ghi)

* displacement (hằng số + nội dung thanh ghi) (1 truy cập bộ nhớ)

* implicit (0 truy cập bộ nhớ)

57

New cards

thứ tự nhanh chậm của các cách đánh mode địa chỉ

* immediate

* thanh ghi

* direct

* thanh ghi gián tiếp

* indirect

* thanh ghi

* direct

* thanh ghi gián tiếp

* indirect

58

New cards

displacement

\[BX\]15

\[BX +15\]

\[BX +15\]

59

New cards

MOV AL, OxAB

MOV AH, OxCD

MOV AH, OxCD

CDAB

60

New cards

thanh ghi

có 2 loại

61

New cards

thanh ghi cờ trạng thái

* lưu trạng thái kết quả của CPU sau khi thực hiện mỗi lệnh

* mỗi cờ 1 bit, tập trung tất cả vào 1 thanh ghi

* các loại cờ:

* Sign: 1 nếu là số âm

* Zero: 1 nếu kết quả là 0

* Carry: 1 nếu có nhớ ra ngoài

* Equal: nếu ss hai số = nhau thì 1

* overflow: 1 nếu + số bù 2 k đủ bit

* Harry- carry

* mỗi cờ 1 bit, tập trung tất cả vào 1 thanh ghi

* các loại cờ:

* Sign: 1 nếu là số âm

* Zero: 1 nếu kết quả là 0

* Carry: 1 nếu có nhớ ra ngoài

* Equal: nếu ss hai số = nhau thì 1

* overflow: 1 nếu + số bù 2 k đủ bit

* Harry- carry

62

New cards

pipelining (kỹ thuật ống dẫn)

* tăng tốc độ xử lý mà không đụng đến phần cứng

* có n câu lệnh, pp p bước thì tổng có p+n-1 bước

* có n câu lệnh, p bước, k pp thì có p\*n bước

* trường hợp ss pp và k pp mà k thay đổi CPI, f thì sẽ là (p\*n)/(p+n-1) và khi n rất lớn thì đáp án tới p

* trường hợp có thay đổi: (CPI_KPL x fPL / CLP_PL x f_KPL).

\

* có n câu lệnh, pp p bước thì tổng có p+n-1 bước

* có n câu lệnh, p bước, k pp thì có p\*n bước

* trường hợp ss pp và k pp mà k thay đổi CPI, f thì sẽ là (p\*n)/(p+n-1) và khi n rất lớn thì đáp án tới p

* trường hợp có thay đổi: (CPI_KPL x fPL / CLP_PL x f_KPL).

\

63

New cards

rủi ro pipeline (3 loại)

* **rủi ro về tài nguyên**: có 2 hay nhiều lệnh truy cập vào tài nguyên phần cứng (CPU, bộ nhớ, I/O, bus) cùng một lúc →giải quyết: *dời*

* **rủi ro về dữ liệu**: xảy ra khi câu lệnh sau cần dùng kết quả của câu lệnh trước nhưng khi cần dùng thì câu lệnh trước chưa có kết quả → giải quyết : *dời*

* **rủi ro về điều khiển**: là rủi ro khi trong CT có lệnh nhảy hoặc lệnh rẽ nhánh (gọi CT con, vòng lặp) → do thực hiện pp nên sẽ có 1 số câu lệnh k mong muốn đc thực hiện → giải quyết: *sau kiểm tra mới pp*

* **rủi ro về dữ liệu**: xảy ra khi câu lệnh sau cần dùng kết quả của câu lệnh trước nhưng khi cần dùng thì câu lệnh trước chưa có kết quả → giải quyết : *dời*

* **rủi ro về điều khiển**: là rủi ro khi trong CT có lệnh nhảy hoặc lệnh rẽ nhánh (gọi CT con, vòng lặp) → do thực hiện pp nên sẽ có 1 số câu lệnh k mong muốn đc thực hiện → giải quyết: *sau kiểm tra mới pp*

64

New cards

bộ nhớ máy tính

* địa điểm: trong - ngoài

* dung lượng: word - byte

* đơn vị truy cập: từ - block

* dung lượng: word - byte

* đơn vị truy cập: từ - block

65

New cards

phương thức truy cập bộ nhớ (4)

1. truy cập ***tuần tự*** (băng cát sét)

2. truy cập ***trực tiếp*** (theo từng file, từng thư mục) (phần cứng)

3. truy cập ***random***: truy cập ngẫu nhiên theo từng byte, từng từ (bộ nhớ trong)

4. ***Associative***: truy cập kết hợp (cache)

66

New cards

performance của bộ nhớ

* thời gian truy cập: từ lúc gửi yêu cầu cho đến lúc nhận lại được dl

* khoảng thời gian giữa hai lần truy cập lt lớn hơn rất nhiều tgian truy cập vì còn đợi bộ nhớ reset

* tốc độ dữ liệu truyền bit/s, byte/s

* khoảng thời gian giữa hai lần truy cập lt lớn hơn rất nhiều tgian truy cập vì còn đợi bộ nhớ reset

* tốc độ dữ liệu truyền bit/s, byte/s

67

New cards

các loại bộ nhớ

1. bộ nhớ bán dẫn **(SSD, RAM,ROM, thẻ nhớ)**

2. bộ nhớ từ

3. bộ nhớ quang

4. bộ nhớ quang - từ

68

New cards

đặc tính vật lý của hệ thống bộ nhớ

* volatile: khi mất nguồn là mất dữ liệu (RAM)

* non volatile: khi mất nguồn k mất dữ liệu (ổ chứng, CD, DVD)

* erasable: có thể ghi nội dung mới vào (RAM, ổ cứng, thẻ nhớ)

* nonerasable: không thể ghi nội dung mới vào (RAM)

* non volatile: khi mất nguồn k mất dữ liệu (ổ chứng, CD, DVD)

* erasable: có thể ghi nội dung mới vào (RAM, ổ cứng, thẻ nhớ)

* nonerasable: không thể ghi nội dung mới vào (RAM)

69

New cards

thứ bậc của các bộ nhớ

* thanh ghi

* cache (chia thành 2)

* bộ nhớ chính

* đĩa từ

* magnetic type

*càng xuống dưới càng xa CPU, tốc độ giảm dần, dung lượng tăng dần*

tốc độ truy cập nhanh, giá cao hơn

dung lượng lớn hơn, giá thành nhỏ hơn (cost per bit)

dung lượng càng lớn, thời gian truy cập càng chậm

***• Tăng công suất • Tăng thời gian truy cập • Giảm chi phí trên mỗi bit • Giảm tần suất truy cập của bộ nhớ của bộ xử lý***

* cache (chia thành 2)

* bộ nhớ chính

* đĩa từ

* magnetic type

*càng xuống dưới càng xa CPU, tốc độ giảm dần, dung lượng tăng dần*

tốc độ truy cập nhanh, giá cao hơn

dung lượng lớn hơn, giá thành nhỏ hơn (cost per bit)

dung lượng càng lớn, thời gian truy cập càng chậm

***• Tăng công suất • Tăng thời gian truy cập • Giảm chi phí trên mỗi bit • Giảm tần suất truy cập của bộ nhớ của bộ xử lý***

70

New cards

cache memory

* tốc độ truy cập cao, nằm giữa CPU và bộ nhớ chính

* không cần qua ht bus

* CPU truy cập cache theo hình thức ngẫu nhiên

* cache hit: khi CPU cần và từ đó có trong cache

* cache miss: khi CPU cần và từ đó không có trong cache thì cache ra bộ nhớ chính lấy, mỗi lần lấy 1 block (truy cập kết hợp)

* CPU tới cache: nhanh

* cache tới MM: theo từng block, chậm

* không cần qua ht bus

* CPU truy cập cache theo hình thức ngẫu nhiên

* cache hit: khi CPU cần và từ đó có trong cache

* cache miss: khi CPU cần và từ đó không có trong cache thì cache ra bộ nhớ chính lấy, mỗi lần lấy 1 block (truy cập kết hợp)

* CPU tới cache: nhanh

* cache tới MM: theo từng block, chậm

71

New cards

Thuật toán ánh xạ trong địa chỉ cache

* ánh xạ block nào với line nào

* ánh xạ trực tiếp: tag/line/word

tính số block trong 1 line →số bit tag

block j qua line i: i=j mod n (với n là số line)

* ánh xạ kết hợp toàn phần: tag/word

* ánh xạ từng phần: tag/set/word

block j →set i: i=j mod n (n là số set)

block K - way SA: 1 set có K line

* ánh xạ trực tiếp: tag/line/word

tính số block trong 1 line →số bit tag

block j qua line i: i=j mod n (với n là số line)

* ánh xạ kết hợp toàn phần: tag/word

* ánh xạ từng phần: tag/set/word

block j →set i: i=j mod n (n là số set)

block K - way SA: 1 set có K line

72

New cards

replacement policy

* thường xuyên ít được sử dụng: LFU →cache hit tương đối cao

* LRU: ít được sử dụng →cache hit cao nhất

* FIFO

* random →cache hit thấp nhất

* LRU: ít được sử dụng →cache hit cao nhất

* FIFO

* random →cache hit thấp nhất

73

New cards

write policy

* write through: mỗi lần CPU ghi dl vào cache đều cập nhật ra bộ nhớ chính

* write back: CPU ghi 2 lần liên tiếp vào 1 line thì dl cũ được lưu vào MM →được dùng nhiều hơn

cờ Dirty: line đó đang lưu dl chưa được lưu vào MM

* write back: CPU ghi 2 lần liên tiếp vào 1 line thì dl cũ được lưu vào MM →được dùng nhiều hơn

cờ Dirty: line đó đang lưu dl chưa được lưu vào MM

74

New cards

bộ nhớ trong

là bộ nhớ bán dẫn

75

New cards

semiconductor MM

* thành phần cơ bản: tế bào nhớ (lưu trữ 1 bit)

* địa chỉ cần đọc, tín hiệu đọc : đọc

* địa chỉ cần ghi, tín hiệu ghi, dl cần ghi: ghi

* địa chỉ cần đọc, tín hiệu đọc : đọc

* địa chỉ cần ghi, tín hiệu ghi, dl cần ghi: ghi

76

New cards

phân biệt RAM, ROM

RAM ROM

mất nguồn → mất dl mất nguồn →vẫn còn dl

đọc, ghi chỉ đọc

mất nguồn → mất dl mất nguồn →vẫn còn dl

đọc, ghi chỉ đọc

77

New cards

các loại ROM

1. PROM: lập trình được 1 lần = công cụ của nsx

2. EPROM: ghi dl vào đc, xóa đc và xóa = tia cực tím. Muốn ghi 1 byte/1 từ thì cx phải xóa hết con chip

3. EEPROM: đắt nhất, chứa hệ điều hành trong đth thông minh, xóa = xung điện. Muốn xóa 1 byte/ 1 từ thì xóa cái đó thôi

4. Flash Memory: nằm trong thẻ nhớ, xóa = xung điện, xóa theo từng khối

5. ROM

78

New cards

giống và khác nhau của DRAM (Ram động), SRAM (ram tĩnh)

giống: DRAM, SRAM mất nguồn →mất dl

DRAM:

* 1 tế bào nhớ gồm 1 bóng bán dẫn và 1 tụ điện (bit 0, bit 1)

* vẫn có khả năng bị mất dl dù đang có nguồn (do tụ điện)

* cơ chế làm tươi dl

* dl của DRAM lớn hơn

\

SRAM

* 1 tế bào nhớ gồm 4,6 bóng bán dẫn

* tốc độ truy cập nhanh hơn

* giá cao hơn

DRAM:

* 1 tế bào nhớ gồm 1 bóng bán dẫn và 1 tụ điện (bit 0, bit 1)

* vẫn có khả năng bị mất dl dù đang có nguồn (do tụ điện)

* cơ chế làm tươi dl

* dl của DRAM lớn hơn

\

SRAM

* 1 tế bào nhớ gồm 4,6 bóng bán dẫn

* tốc độ truy cập nhanh hơn

* giá cao hơn

79

New cards

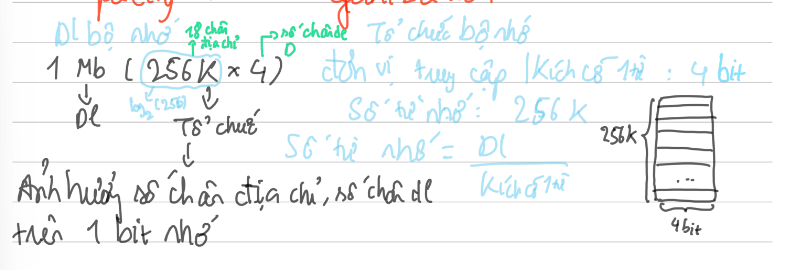

dung lượng bộ nhớ và tổ chức bộ nhớ

80

New cards

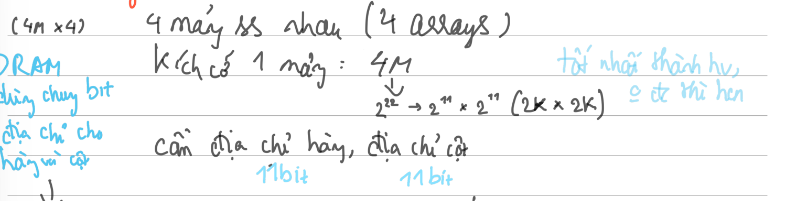

DRAM

DRAM dùng chung bit địa chỉ hàng và cột →giảm được số chân đia chỉ nhưng kết nối phức tạp

Nhược điểm: tốn thêm chu kỳ để lấy cột sau khi lấy hàng mà chu kỳ rất nhỏ nên ưu >nhược

Nhược điểm: tốn thêm chu kỳ để lấy cột sau khi lấy hàng mà chu kỳ rất nhỏ nên ưu >nhược

81

New cards

MM organization

82

New cards

cơ chế sửa lỗi

* hamming error correcting code: chỉ dùng được trong trường hợp 1 lỗi

***C = log2D +1***

C: check bits

D: data bits

* ***C= log2D+2***

tổng số bit 1 là chẵn

* DED: có lỗi mà bit tổng không đổi → có 2 lỗi

***C = log2D +1***

C: check bits

D: data bits

* ***C= log2D+2***

tổng số bit 1 là chẵn

* DED: có lỗi mà bit tổng không đổi → có 2 lỗi

83

New cards

tổ chức DRAM nâng cao

DDR DRAM có thể gửi 2 đơn vị dữ liệu trong 1 chu kỳ

84

New cards

magnetic disk

* ổ từ: HDD: lớp tráng là lớp từ

* ổ cứng: hình tròn, 1 chồng ổ đĩa chồng lên nhau

* quay mới hoạt động được

* đàu đọc/ghi: đi đường thẳng, di chuyển giữa các track thì bk là đường đi lớn nhất

* sectors: đơn vị đọc/ghi của ổ cứng

* ổ cứng: hình tròn, 1 chồng ổ đĩa chồng lên nhau

* quay mới hoạt động được

* đàu đọc/ghi: đi đường thẳng, di chuyển giữa các track thì bk là đường đi lớn nhất

* sectors: đơn vị đọc/ghi của ổ cứng

85

New cards

disk performance parameters

* thời gian tìm: tgian để đầu ghi tới đúng track

* rotational delay: tgian để ổ đĩa quay để tới đúng sectors

* accesstime = tgian tìm +rotational delay

* transfer time: thời gian để đọc/ghi

* rotational delay: tgian để ổ đĩa quay để tới đúng sectors

* accesstime = tgian tìm +rotational delay

* transfer time: thời gian để đọc/ghi

86

New cards

đặc tính vật lý của ổ HDD (ổ đĩa cứng)

* head motion

* fixed head: mỗi track 1 đầu đọc riêng

* movable head

* Disk portability

* không thể tháo trời trong khi đang hoạt động

* có thể……………….

* fixed head: mỗi track 1 đầu đọc riêng

* movable head

* Disk portability

* không thể tháo trời trong khi đang hoạt động

* có thể……………….

87

New cards

RAID

* dùng nhiều ổ đĩa cùng 1 lúc →tăng dl, tăng tốc độ truy cập, sửa lỗi, back up dl

* có 7 bậc RAID

* striping: lưu dl trải dài, level O, yêu cầu N đĩa, không cso back up

* mirroring: đắt nhắt, an toàn nhất, level 1, yêu cầu 2N đĩa, có back up

* parallel access: level 2,3; 1 ứng dụng có thể truy cập nhiều ổ. Level 2 yêu cầu N+m, m=log2N +1 để sửa lỗi, level 3 yêu cầu N+1 đĩa

* independent access: nhiều ứng dụng có thể truy cập cùng 1 lúc nhưng mỗi ứng dụng 1 đĩa, level 4,5,6. Level 4,5 yêu cầu N+1 đĩa. Level 6 yêu cầu N+2 đĩa. Level 5,6 không lưu tập trung 1 ổ mà dàn trãi trên tất cả

* có 7 bậc RAID

* striping: lưu dl trải dài, level O, yêu cầu N đĩa, không cso back up

* mirroring: đắt nhắt, an toàn nhất, level 1, yêu cầu 2N đĩa, có back up

* parallel access: level 2,3; 1 ứng dụng có thể truy cập nhiều ổ. Level 2 yêu cầu N+m, m=log2N +1 để sửa lỗi, level 3 yêu cầu N+1 đĩa

* independent access: nhiều ứng dụng có thể truy cập cùng 1 lúc nhưng mỗi ứng dụng 1 đĩa, level 4,5,6. Level 4,5 yêu cầu N+1 đĩa. Level 6 yêu cầu N+2 đĩa. Level 5,6 không lưu tập trung 1 ổ mà dàn trãi trên tất cả

88

New cards

SSD (ổ bán dẫn)

flash- memory based SSD

* NOR flash memory

* đọc, ghi theo byte

* NAND flash memory

* đọc ghi theo từng block nhỏ, dùng trong usb, memory card, ssds

* NOR flash memory

* đọc, ghi theo byte

* NAND flash memory

* đọc ghi theo từng block nhỏ, dùng trong usb, memory card, ssds

89

New cards

so sánh SSD và HDD

SSD HDD

nhanh hơn dl lớn hơn

bền hơn

k có ồn

đắt hơn

nhanh hơn dl lớn hơn

bền hơn

k có ồn

đắt hơn

90

New cards

optical memory: ổ quang (bộ nhớ ngoài)

* làm bằng nhựa, tráng lớp bảo vệ

* dùng tia sáng để ghi dl

* DL DVD cao hơn CD

* dùng bước sóng khác nhau để ghi → DL khác nhau → giá khác nhau

* dùng tia sáng để ghi dl

* DL DVD cao hơn CD

* dùng bước sóng khác nhau để ghi → DL khác nhau → giá khác nhau

91

New cards

các hệ thống nhớ máy tính có thể có ở

* các thanh ghi

* bộ nhớ trong

* bộ nhớ ngoài

* bộ nhớ trong

* bộ nhớ ngoài

92

New cards

93

New cards

vì sao cần dùng module I/O?

vì đơn vị dl khác nhau, tốc độ giữ lý khác nhau giữa máy tính và TBNV

94

New cards

chúc năng của I/O module function

* giao tiếp với bộ xử lý

* giao tiếp với TBNV

* đệm dl

* control and timing

* kiểm tra, phát hiện lỗi trong quá trình giao tiếp của hai bên

*có hỗ trợ DMA, ngoài giao tiếp với CPU, module I/O còn giao tiếp với bộ nhớ*

* giao tiếp với TBNV

* đệm dl

* control and timing

* kiểm tra, phát hiện lỗi trong quá trình giao tiếp của hai bên

*có hỗ trợ DMA, ngoài giao tiếp với CPU, module I/O còn giao tiếp với bộ nhớ*

95

New cards

I/O commands

* lệnh ktra

* lệnh đk

* lệnh đọc

* lệnh ghi

* lệnh đk

* lệnh đọc

* lệnh ghi

96

New cards

I/O mapping

* bản đồ bộ nhớ: I/O như 1 ô nhớ trong bộ nhớ để đánh địa chỉ

* Isolated I/O: I/O tách biệt

dùng 1 vùng nhớ riêng biệt (đánh địa chỉ cho I/O riêng biệt, k liên quan đến bộ nhớ)

cần có lệnh đọc ghi bộ nhớ và đọc ghi I/O riêng biệt

* Isolated I/O: I/O tách biệt

dùng 1 vùng nhớ riêng biệt (đánh địa chỉ cho I/O riêng biệt, k liên quan đến bộ nhớ)

cần có lệnh đọc ghi bộ nhớ và đọc ghi I/O riêng biệt

97

New cards

Cơ chế thực hiện I/O (3 loại)

1. programmed I/O: dùng trong các máy không có ngắt

1. CPU phải giám sát hoàn toàn các hoạt động của TBNV

2. gây lãng phí việc sử dụng CPU

2. Interrupt -driven I/O: sử dụng trong những ht có ngắt, TBNV làm xong thì báo về = 1 cái ngắt, CPU không cần chờ, có thể làm những tác vụ khác

3. DMA: cho phép module I/O truy cập trực tiếp bộ nhớ, không cần thông qua CPU nhưng vẫn có 1 module hỗ trợ riêng DMA control

98

New cards

sự phát triển của I/O function

1. không có module I/O

2. programmed I/O

3. ngắt I/O

4. DMA

5. module I/O mạnh như 1 bộ xử lý

6. module I/O mạnh như 1 máy tính

99

New cards

parallel orgainizations

* 4 loại:

* SISD: xử lý đơn câu lệnh trên đơn dl

* SIMD: xử lý đơn câu lệnh trên đa dl (mảng, vecto)

* MISD: xử lý nhiều câu lệnh trên dl đơn

* MIMD: xử lý nhiều câu lệnh trên dl đa →xử lý ss

* nhiều core chung bộ nhớ

* ***SMP***

* NUMA

* nhiều core khác bộ nhớ

* SISD: xử lý đơn câu lệnh trên đơn dl

* SIMD: xử lý đơn câu lệnh trên đa dl (mảng, vecto)

* MISD: xử lý nhiều câu lệnh trên dl đơn

* MIMD: xử lý nhiều câu lệnh trên dl đa →xử lý ss

* nhiều core chung bộ nhớ

* ***SMP***

* NUMA

* nhiều core khác bộ nhớ

100

New cards

SMP (symmetric multiprocessor)

* nhiều bộ xử lý

* ht đa bộ xử lý đối xứng

* các bộ xử lý có cấu hình, chức năng giống hệt nhau

* các bộ xử lý dùng chung bộ nhớ và các TBNV

* có thể có bộ nhớ đệm tiêng

* ht đa bộ xử lý đối xứng

* các bộ xử lý có cấu hình, chức năng giống hệt nhau

* các bộ xử lý dùng chung bộ nhớ và các TBNV

* có thể có bộ nhớ đệm tiêng

Explore top notes

Personality 210 Psychology Notes (Part 3) Continuing Traits and Trait Traditions

Updated 1344d ago0.0(0)

Personality 210 Psychology Notes (Part 3) Continuing Traits and Trait Traditions

Updated 1344d ago0.0(0)