15 - Hardware and Virtual Machines

1/17

There's no tags or description

Looks like no tags are added yet.

Name | Mastery | Learn | Test | Matching | Spaced |

|---|

No study sessions yet.

18 Terms

Describe Reduced Instruction Set Computers (RISC). [6]

Uses simple instructions

Uses fixed length instructions

Instructions only require one clock cycle

Uses many registers

Makes use of pipelining

Hardwired CU

Describe Complex Instruction Set Computers (CISC). [9]

Uses many instruction formats

Uses variable length instructions

Makes use of different addressing modes

Uses few registers

Has a large instruction set

Requires complex circuits

Frequently uses cache

Instructions (converted to sub-instructions that) may require many clock cycles

Programmable CU

Describe interrupt handling on RISC and CISC processors. [4]

Once the processor detects an interrupt at the start/end of the fetch-execute cycle

... the current program is temporarily stopped and the status of each register stored on the stack.

After the interrupt has been serviced/the Interrupt Service Register (ISR) has been executed ...

... the registers can be restored to its original status before the interrupt was detected // ... the data can be restored from the stack.

Describe the importance and use of pipelining in RISC processors. [6]

Pipelining allows several instructions to be processed simultaneously / concurrently

...therefore, increasing the CPU instruction throughout / the number of instructions completed per unit of time.

Instructions are divided into 5 stages

Each instruction stage / subtask is completed during one clock cycle

No two instructions can execute their same stage of instruction / subtask at the same clock cycle.

...e.g. while one instruction is being decoded, the next instruction can be fetched, etc.

Explain how pipelining affects interrupt handling. [4]

Pipelining adds an additional complexity // there could be a number of instructions still in the pipeline when the interrupt is received

All the instructions currently in operation are usually discarded except for the last one/the one at write back

... the interrupt handler routine is applied to the remaining instruction.

Once the interrupt has been serviced the processor can restart with the next instruction in the sequence.

Describe the Single Instruction, Single Data (SISD) computer architecture. [3]

Contains one processor, a control unit and a memory unit

Executing a single instruction from a single source

Executes instructions sequentially

Describe the Single Instruction, Multiple Data (SIMD) computer architecture. [3]

Performs the same operation on multiple different data streams simultaneously.

The instructions can be performed sequentially, taking advantage of pipelining.

Parallel computers with multiple processors.

Describe the Multiple Instruction, Single Data (MISD) computer architecture. [3]

Performs different operations on the same data stream.

Each processor works on the same data stream independently.

Parallel computers with multiple processors.

Describe the Multiple Instruction, Multiple Data (MIMD) computer architecture. [3]

Contains many processors

Processors operate asynchronously / independently

Can execute different instructions on different data sets

Describe massively parallel computers. [4]

A large number of computer processors / separate computers connected together

...simultaneously performing a set of coordinated computations // collaborative processing

network infrastructure

communicate using a message interface / by sending messages.

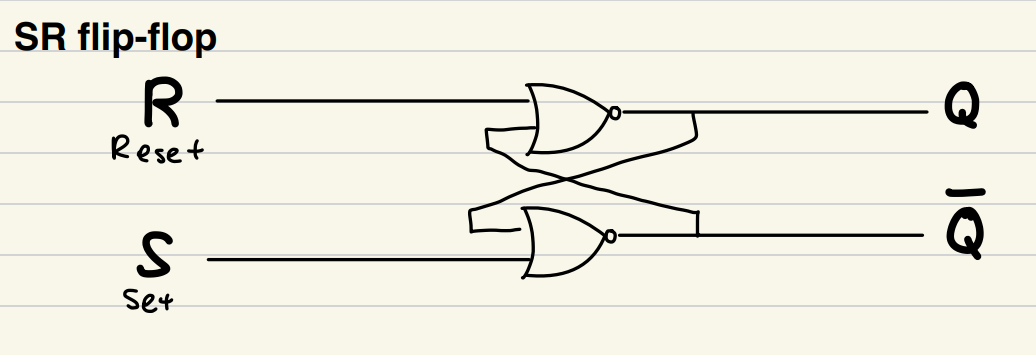

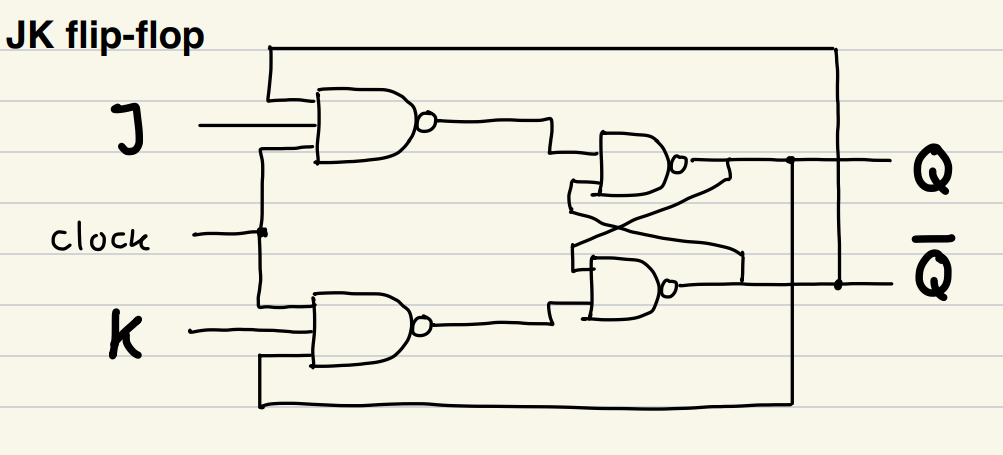

State the purpose of a flip-flop circuit. [1]

The purpose of a flip-flop is to store a binary digit / (single) bit.

Draw the circuit diagram for an SR flip-flop. [1]

Draw the circuit diagram of a JK flip-flop. [1]

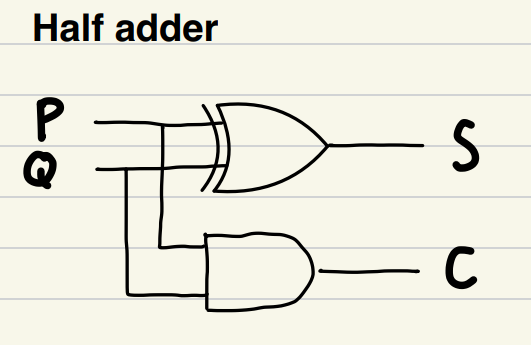

Draw the circuit diagram of a half adder and write an expression for each of the outputs. [3]

S = P XOR Q

C = P AND Q

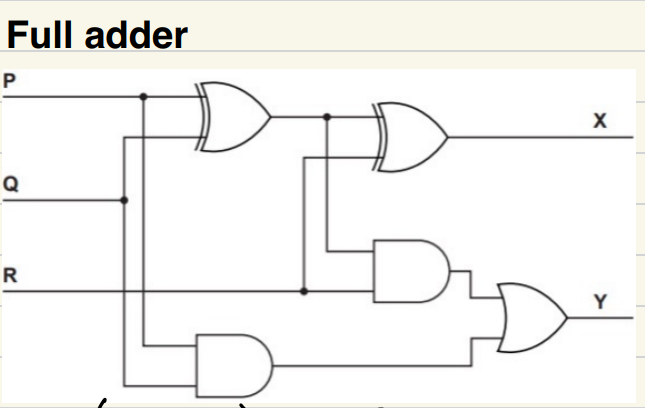

Draw the circuit diagram of a full adder and write an expression for each of the outputs. [3]

X = (P XOR Q) XOR R

Y = ((P XOR Q) AND R) OR (P AND Q)

Describe virtual machines. [3]

The emulation of a computer system / hardware and/or software

...using a host computer system.

Using guest operating system(s) for emulation.

Describe the benefits of virtual machines. [6]

Multiple guest operating systems / VMs can be used on the same computer.

Different instruction set architectures can be emulated on a single computer.

A virtual machine can crash without affecting the host machine.

There are security benefits // Trying a piece of suspicious software and if it is / has a virus, it will only infect the virtual machine.

Cost savings due to not needing to purchase extra hardware.

Can run legacy applications that are currently incompatible.

Describe the drawbacks of virtual machines. [6]

A virtual machine is less efficient / has poorer performance than real machines because of extra load on the host computer

Performance of the guest system cannot be adequately measured.

A virtual machine may be affected by any weaknesses of the host machine.

Costly and/or complex to maintain / implement / manage.

Cannot emulate new hardware

...because the hardware may have been developed since the virtual machine was developed.