ECE 2020 Exam 2

1/46

There's no tags or description

Looks like no tags are added yet.

Name | Mastery | Learn | Test | Matching | Spaced | Call with Kai |

|---|

No analytics yet

Send a link to your students to track their progress

47 Terms

One’s complement

Flip each bit into a binary number, results in redundant numbers for zero

Two’s complement

Flip the sign of each bit

Add +1

Ignore overflow

Range of numbers for unsigned

0 to 2N-1

Range of numbers for signed

-2N-1 to 2N-1-1

Overflow

A number can’t be represented by the available number of bits, or for signed, there is a mismatch in the arithmetic between signs

Combinational logic

Outputs are determined by the input combination

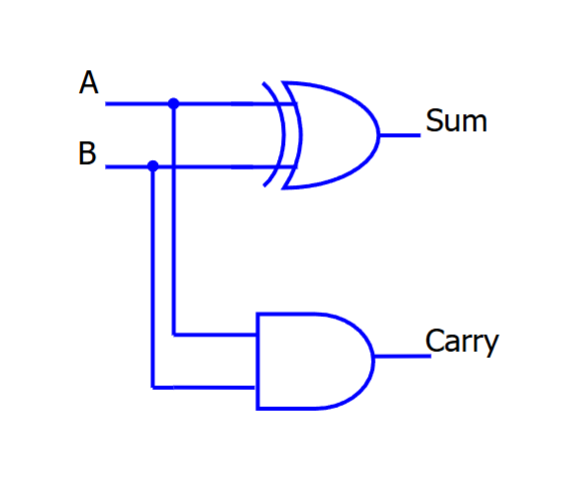

Half adder

S = A XOR B

C = AB

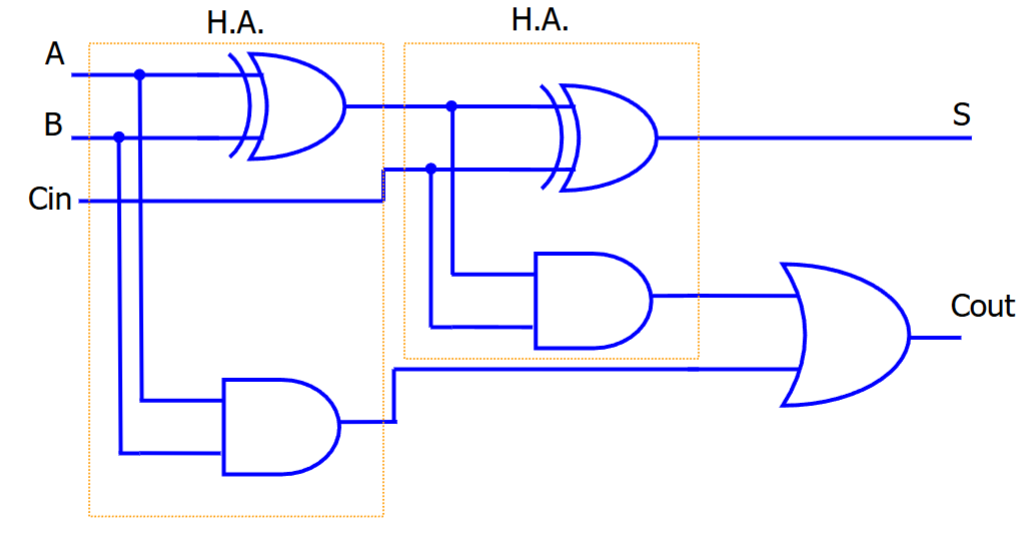

Full adder

S = Cin XOR A XOR B

Cout = AB + Cin(A XOR B)

Ripple adder

Multiple full adders in series, carry-out of each full adder is connected to the carry-in of the next

Cascading carry lookahead adder

Faster than ripple adder

Decoder

n to m line, where m = 2n, all outputs are low except one corresponding to the binary value of the inputs

Enable

Turn on outputs or leaves them off

Any boolean functions can be implemented using a

Decoder and OR gates by ORing together the function’s minterms

Encoder

m to n line encoder, m = 2n

Priority encoder

Takes the input of 1 with the highest index and translates directly to the output

Multiplexer

Selects betwen one of N inputs to connect to output with selector bits

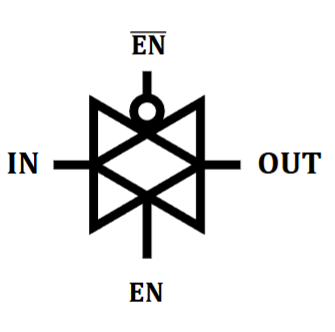

Transmission gates

Allows signals to pass in both directions or blocks them when inactive

How can you implement a mux?

WIth pass gates

Demultiplexer

Takes one input and selects one of many outputs to direct the input

Comparator

Indicates whether A is equal, greater, or less than B

Zero extend

Adds m-n additional zero bits, does not change value of unsigned integers

Sign extend

Adds m-n additional bits equal to the most significant bit of hte input, does not change value of 2’s complement integers

Shifting left is equivalent to…

Multiplying by 2

Shifting right is equivalent to….

Dividing by 2

A transmission gate can be used to…

Set the state

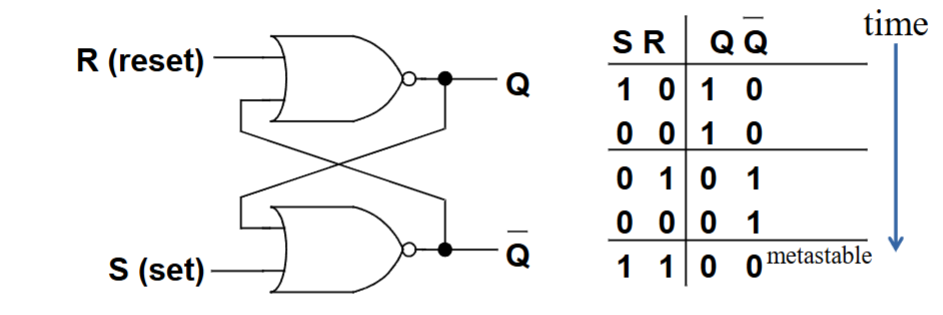

SR latch

Utilize NORs, R on top.

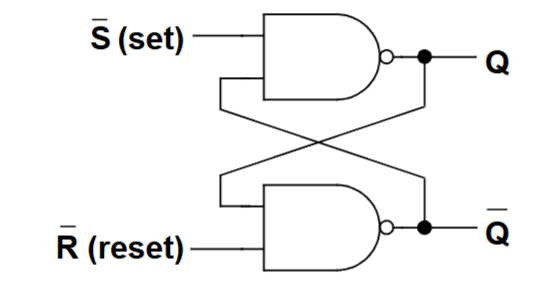

S’R’ latch

Utilize NANDs, S’ on top

How to add an enable line to SR latch?

With NOR gates: use two AND gates prior

With NAND gates: use two NAND gates prior

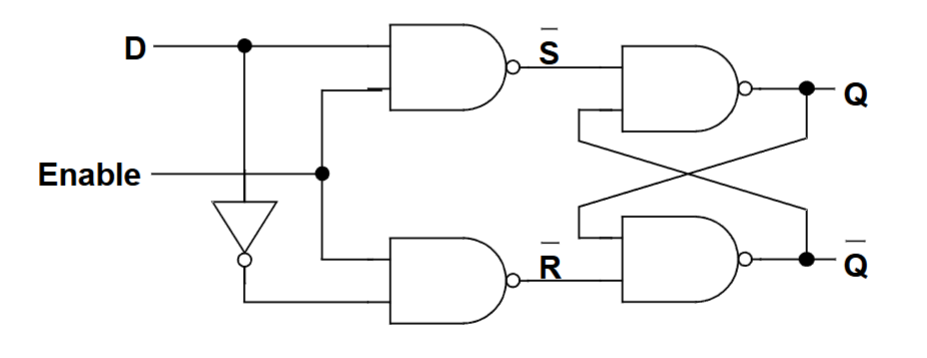

D latch

Same as S’R’ latch essentially, but only driven by D (needs additional inverter) and two additional NAND gates

Transparent/level-sensitive

Output follows the input

Leader and follower

Separates input from the output, leader accepts input while follower gives output

Flip-flop

Edge triggered, single bit storage

Register

A device that stores a value, updated on each clock cycle

A flip-flop is a 1 bit register, can form multiple bit register by grouping flip flops together

Mealy machine

FSM where output depends on current input AND state

Moore machine

Output depends only on current state

How to create an FSM with hardware?

State transition table with present state, input, next state, and output

Turn into a K-map

Express a boolean function

Make gates

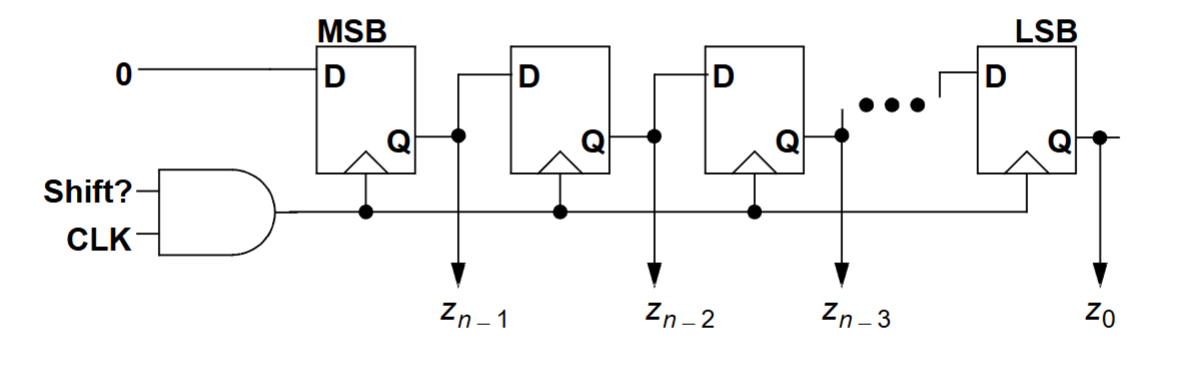

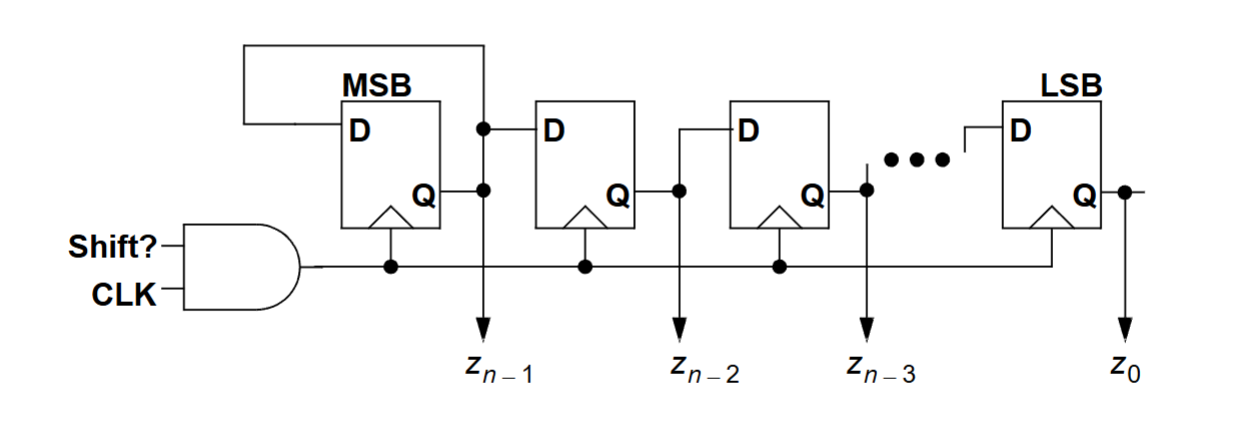

Shift register

Takes stored bits and moves them up a significnt bit or down a significant bit

What does a logical shift register look like?

What does arithmetic shift look like?

(the most significant bit is fed into the next flip flop (what the state currently is), in comparison to the logical shift where the MSB is automatically assigned 0

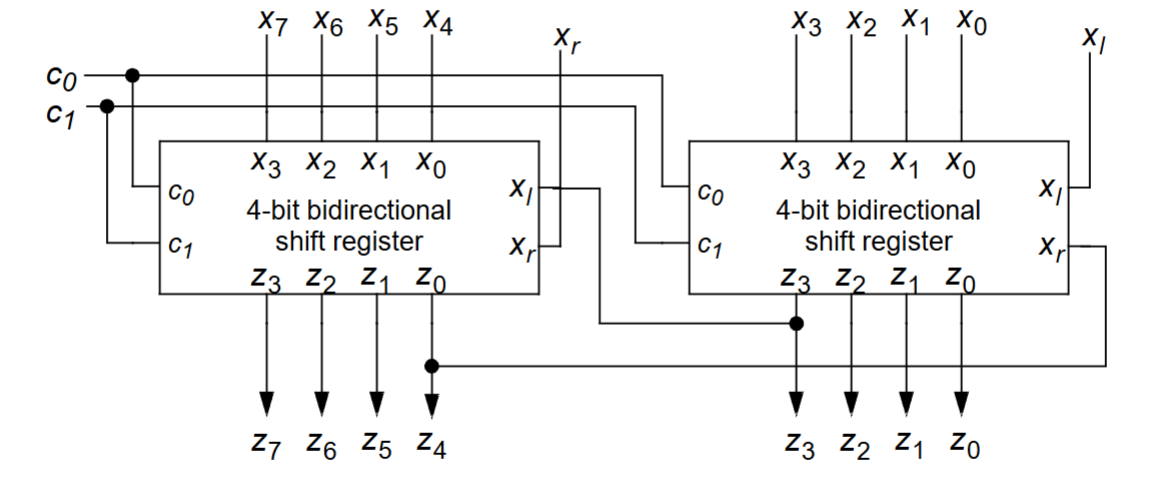

How to chain together shift registers together?

Each shift register handles half of the inputs and outputs

Control inputs —> select the operating mode (hold, shift left, shift right, or parallel load)

X_l = shift left serial input, connects to Z0

X_r = shift right serial input, connects to Z4

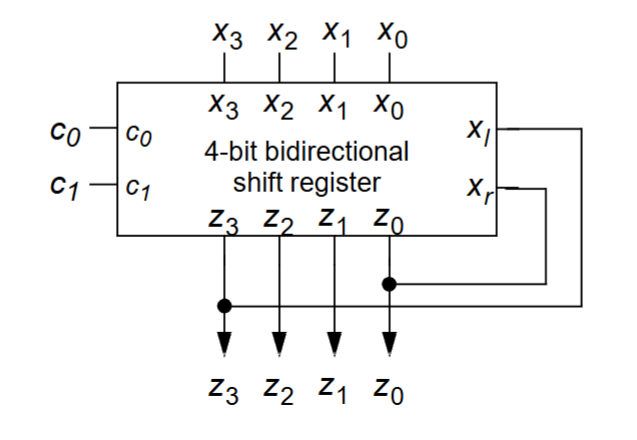

What does a rotate register look like?

X_l = shift left, connects to Z3

X_r = shift right, connects to Z0

(OPPOSITE OF TYPICAL SHIFT REGISTER)

Counter

Incrememts an n-length binary number each clock cycle

Ripple counter

Connects the output to the clock.

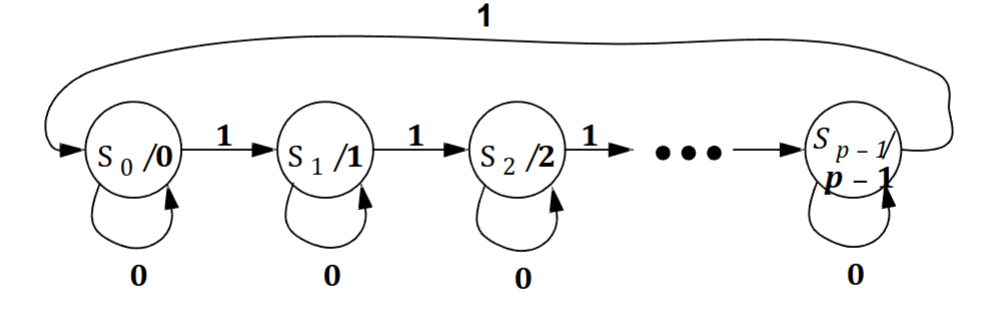

Modulo-p counter

S(t+1) = (S(t) + x) % p

How many states can a counter represent

2N states

When a counter reaches its last state, what does it do?

Wraps back to 0 and repeats

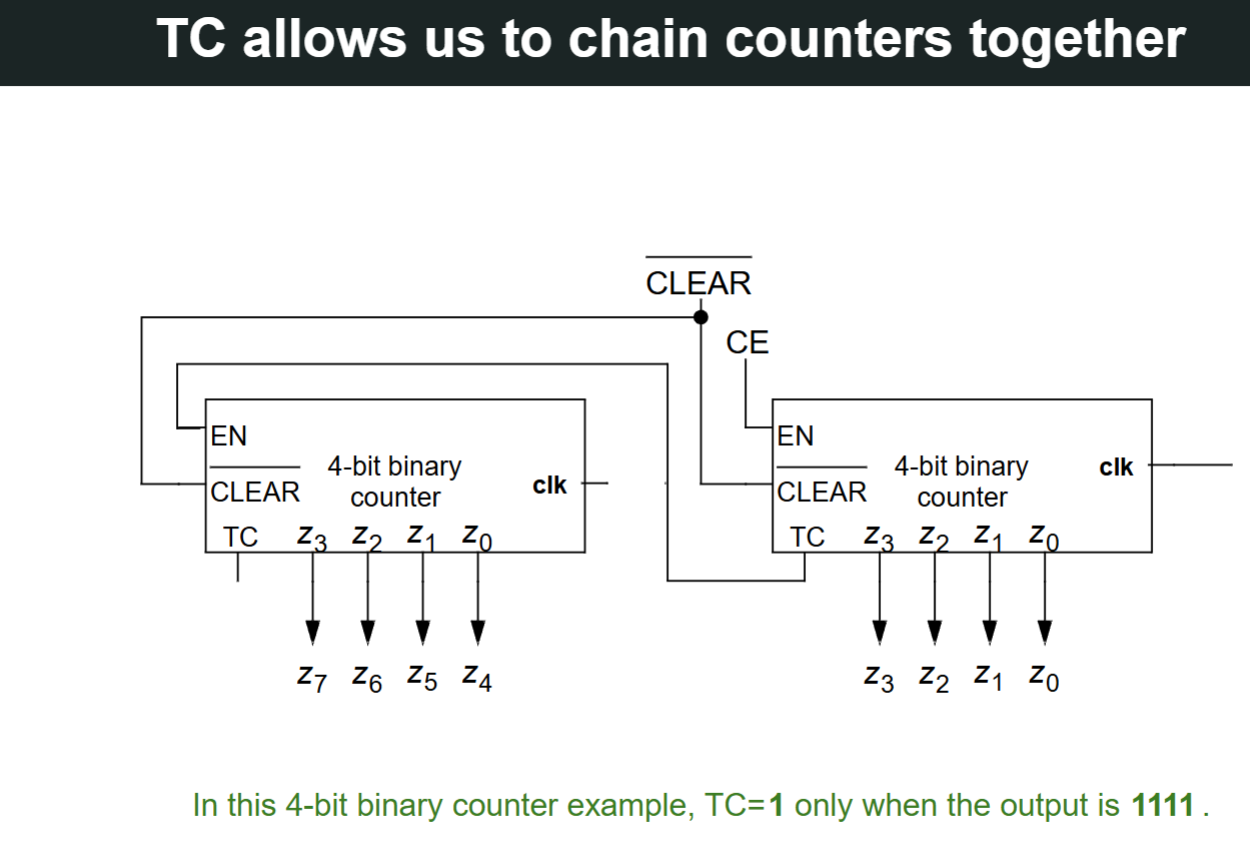

What does a terminal count output do?

Enables resetting at a specific time, enables chaining of counters together. TC of the first counter will connect to enable of the subsequent one