egzamin mikro pytania

0.0(0)

Card Sorting

1/128

There's no tags or description

Looks like no tags are added yet.

Study Analytics

Name | Mastery | Learn | Test | Matching | Spaced |

|---|

No study sessions yet.

129 Terms

1

New cards

Blok rejestrów pomocniczych ARx procesora TMS32C50 służy do:

\+ Adresowania natychmiastowego wewnętrznej pamięci danych

\+Adresowania pośredniego wewnętrznej pamięci danych

\+Wspomagają Akumulator procesora w operacjach logicznych i stałoprzecinkowych operacjach arytmetycznych

\+Adresowania pośredniego wewnętrznej pamięci danych

\+Wspomagają Akumulator procesora w operacjach logicznych i stałoprzecinkowych operacjach arytmetycznych

2

New cards

Architektura ARM Cortex_M4 składa się z następujących bloków głównych:

\+Magistral systemowych

\+ Pamięci i układów peryferyjnych

\+AIC (kontroler przerwań wektorowych)

\+ Rdzenia procesora ARMv4DTMI

\+ Pamięci i układów peryferyjnych

\+AIC (kontroler przerwań wektorowych)

\+ Rdzenia procesora ARMv4DTMI

3

New cards

Makrodefinicja \*AT19C_PIOB_SODR = AT91C_PIO_PB23 wymaga:

\+ Definicji IO_SODR: #define AT91C_PIOB_SODR ((AT91_REG\*) 0xFFFFF600)

\+ Definicji bitu: #define AT91C_PIO_PB23 ((unsigned int) 1 << 23)

\+ Definicji wskaźnika: typedef unsigned int AT91_REG

\+ Definicji bitu: #define AT91C_PIO_PB23 ((unsigned int) 1 << 23)

\+ Definicji wskaźnika: typedef unsigned int AT91_REG

4

New cards

Startup układu SAM7 (początek pracy), zawiera:

\+ Oprogramowanie (konfiguracja) układów peryferyjnych procesora, np. zegar, RST, watchdog itp.

\+ Oprogramowanie wektora resetu oraz wektorów przerwań - (dla nieużywanych przerwań umieszczenie pustych funkcji)

\+Konfiguracja pamięci (SRAM, przemapowanie pamięci FLASH, wyczyszczenie pamięci)

\+ Alokacja miejsca na stosy oraz inicjalizacja wskaźników stosów dla wszystkich trybów pracy procesora.

\

Wszystkie odpowiedzi poprawne

\+ Oprogramowanie wektora resetu oraz wektorów przerwań - (dla nieużywanych przerwań umieszczenie pustych funkcji)

\+Konfiguracja pamięci (SRAM, przemapowanie pamięci FLASH, wyczyszczenie pamięci)

\+ Alokacja miejsca na stosy oraz inicjalizacja wskaźników stosów dla wszystkich trybów pracy procesora.

\

Wszystkie odpowiedzi poprawne

5

New cards

Cechy sterownika przerwań dla rodziny AT91SAM7:

a. Przerwania mogą zostać wykorzystane do wyprowadzenia procesora ze stanu uśpienia(idle mode)

b. Przerwania o numerach 2-31 (PID2-PID31) mogą zostać dołączone do urządzeń peryferyjnych (użytkownika) lub portów I/O.

c. Przerwanie o numerze 0 (FIQ) jest zawsze przerwaniem typu FIQ.

d. Sterownik przerwań wykorzystuje zegar systemowy. Zegar doprowadzany jest poprzez moduł PMC (wymaga włączenia).

b. Przerwania o numerach 2-31 (PID2-PID31) mogą zostać dołączone do urządzeń peryferyjnych (użytkownika) lub portów I/O.

c. Przerwanie o numerze 0 (FIQ) jest zawsze przerwaniem typu FIQ.

d. Sterownik przerwań wykorzystuje zegar systemowy. Zegar doprowadzany jest poprzez moduł PMC (wymaga włączenia).

6

New cards

Cechy portu diagnostycznego DBGU (DeBuG Unit):

b. Sygnalizacja popełnionego błędu TXD lub RXD.

c. Analiza poprawności odebranych ramek.

d. Asynchroniczna transmisja danych zgodna ze standardem RS232: 8 bitów danych, jeden bit stopu, jeden bit potwierdzenia ACK.

c. Analiza poprawności odebranych ramek.

d. Asynchroniczna transmisja danych zgodna ze standardem RS232: 8 bitów danych, jeden bit stopu, jeden bit potwierdzenia ACK.

7

New cards

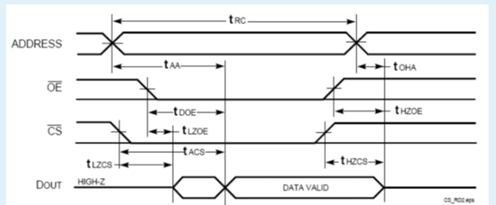

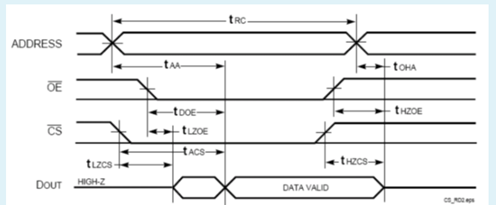

Przebiegi czasowe na rysunku dotyczą:

Odczytu pamięci statycznej SRAM

8

New cards

Do urządzeń systemowych w AT91SAM7 zaliczamy:

a. Sterownik przerwań AIC (Advanced Interrupt Controller)

b. Sterownik DMA (Direct Memory Access)

d. Timery PIT (Periodic Interval Timer), TRTT (Real-Time Timer) oraz WDT (Watchdog Timer)

e. Sterownik pamięci MC (Memory Controller) - Poprawne.

b. Sterownik DMA (Direct Memory Access)

d. Timery PIT (Periodic Interval Timer), TRTT (Real-Time Timer) oraz WDT (Watchdog Timer)

e. Sterownik pamięci MC (Memory Controller) - Poprawne.

9

New cards

Procesor z rodziny ARM

a. Posiada równoległą mnożarkę 32x32 oraz rejestr skalujący umożliwiający wykonywanie operacji z akumulacją - Poprawne.

c. Posiada kilka rejestrów statusowych SPSR (Saved Program Status Register)

e. Posiada 4-bajtową (32-bitową) magistralę adresową

c. Posiada kilka rejestrów statusowych SPSR (Saved Program Status Register)

e. Posiada 4-bajtową (32-bitową) magistralę adresową

10

New cards

Przestrzeń adresowa przyporządkowana portom z rodziny SAM7

a. Znajduje się w górnej przestrzeni adresowej układu SAM7, od adresu 0x1000000 do której mamy dostęp bezpośredni

c. Znajduje się w dolnej przestrzeni adresowej zarezerwowanej dla urządzeń systemowych

c. Znajduje się w dolnej przestrzeni adresowej zarezerwowanej dla urządzeń systemowych

11

New cards

Procesory sygnałowe posiadają kilka cech (niespotykanych w innych procesorach), zapewniających wysoką wydajność:

a. Posiada osiem rejestrów pomocniczych z dedykowaną jednostką arytmetyczną do adresowania pośredniego.

b. Posiada zestaw instrukcji z równoległymi operacjami matematycznymi oraz sprawną realizacją pętli licznikowych

d. Równoległe mnożenie z akumulacją, wykonywane w jednym cyklu pozwalające na realizację różnych operacji, np. splotu

b. Posiada zestaw instrukcji z równoległymi operacjami matematycznymi oraz sprawną realizacją pętli licznikowych

d. Równoległe mnożenie z akumulacją, wykonywane w jednym cyklu pozwalające na realizację różnych operacji, np. splotu

12

New cards

Procedura przerwania od timera PIT-void PIt_Interrupt():

void PIT_interrupt()

{

if(PIT_SR_PITS)

{

…

PIT_PIVR;

}

AIC_EOICR;

}

\

void PIT_interrupt()

{

if(PIT_SR_PITS)

{

…

PIT_PIVR;

}

AIC_EOICR;

}

\

b. Wymaga sprawdzenia, czy przerwanie pochodzi od timera PIT

c. Przekazuje informację o zakończeniu obsługi przerwania po sprawdzeniu flag od innych urządzeń systemowych

c. Przekazuje informację o zakończeniu obsługi przerwania po sprawdzeniu flag od innych urządzeń systemowych

13

New cards

Ścieżka danych procesora VILW danych odpowiada za wykonywanie faktycznych obliczeń. Na przykładzie procesora DSP ścieżka danych zawiera:

a. Pamięć wbudowaną o organizacji macierzowej, akumulator i ALU

c. Akumulator, rejestr skalujący, mnożarkę równoległą oraz pamięć wbudowaną

c. Akumulator, rejestr skalujący, mnożarkę równoległą oraz pamięć wbudowaną

14

New cards

Wektor przerwań to:

a. Tablica zawierająca adresy źródeł przerwań sprzętowych oraz programowych

15

New cards

Rejestry selektorów procesora i486 służą do:

a. Wskazywania deskryptora z adresem bazowym w trybie chronionym

16

New cards

Sterownik przerwań AIC układu SAM7

a. Może wyprowadzić procesor ze stanu uśpienia (idle mode)

b. Obsługuje zgłoszenia żądania przerwania od wewnętrznych układów peryferyjnych generując sygnał IRQ lub FIQ dla jednostki CPU (ARM7)

b. Obsługuje zgłoszenia żądania przerwania od wewnętrznych układów peryferyjnych generując sygnał IRQ lub FIQ dla jednostki CPU (ARM7)

17

New cards

Dostęp do urządzeń zewnętrznych uzyskujemy poprzez rejestry specjalne. Który tryb dotyczy dostępu z wykorzystaniem adresu bazowego:

b. Adres bazowy jest adresem fizycznym początku przestrzeni adresowej układów we/wy:

**pPioSodrRegister = (uint32_t*)0xF0000000; *pPioSodrRegister = (1 << 23);**

c. Adresem bazowym jest adres fizyczny rejestru w górnej części przestrzeni adresowej zarezerwowanej dla układów we/wy:

**pPioSodrRegister = (uint32_t*)0xFFFF630; *pPioSodrRegister = (1 << 23);**

d. Adres bazowy jest adresem fizycznym pierwszego rejestru specjalnego umieszczonego w przestrzeni adresowej zarezerwowanej dla danego układu we/wy:

**#define AT91C_BASE_PIOB ((AT91PS_PIO) 0xFFFF600) AT91_BASE_PIOA->PIO_SODR = 0xFF;**

\

**pPioSodrRegister = (uint32_t*)0xF0000000; *pPioSodrRegister = (1 << 23);**

c. Adresem bazowym jest adres fizyczny rejestru w górnej części przestrzeni adresowej zarezerwowanej dla układów we/wy:

**pPioSodrRegister = (uint32_t*)0xFFFF630; *pPioSodrRegister = (1 << 23);**

d. Adres bazowy jest adresem fizycznym pierwszego rejestru specjalnego umieszczonego w przestrzeni adresowej zarezerwowanej dla danego układu we/wy:

**#define AT91C_BASE_PIOB ((AT91PS_PIO) 0xFFFF600) AT91_BASE_PIOA->PIO_SODR = 0xFF;**

\

18

New cards

Praca i486 w trybie chronionym:

a. Procesor posiada mechanizmy ochrony pamięci oraz dostępu do urządzeń we/wy

b. Występuje mechanizm stronicowania pamięci bazujący na adresie liniowym powstałym w procesie segmentacji pamięci

b. Występuje mechanizm stronicowania pamięci bazujący na adresie liniowym powstałym w procesie segmentacji pamięci

19

New cards

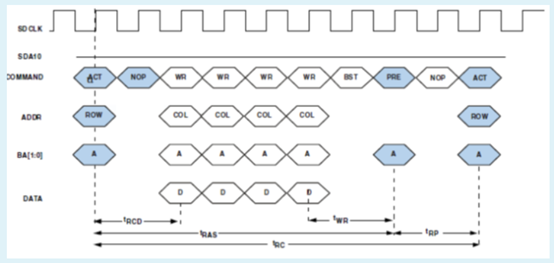

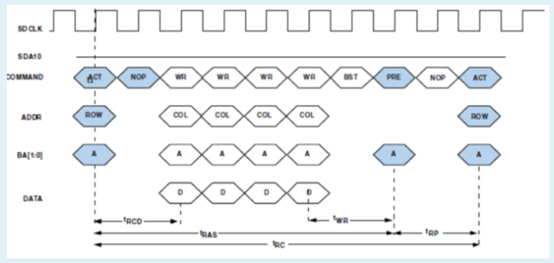

Przedstawione na rysunku przebiegi czasowe:

a. “puste“ cykle oczekiwania (NOP) związane są z szybkością pamięci

b. cykl zapisu do pamięci dynamicznej

d. Po dwóch cyklach od zainicjowania odczytu pamięć wystawia dane na magistralę danych

b. cykl zapisu do pamięci dynamicznej

d. Po dwóch cyklach od zainicjowania odczytu pamięć wystawia dane na magistralę danych

20

New cards

Jednostka centralna procesora DSP TMS320C50 składa się;

b. Równoległej jednostki logicznej (PLU)

c. Równoległej mnożarki arytmetycznej 32-bitowej

d. Rejestrów pomocniczych odwzorowanych w wewnętrznej pamięci RAM

c. Równoległej mnożarki arytmetycznej 32-bitowej

d. Rejestrów pomocniczych odwzorowanych w wewnętrznej pamięci RAM

21

New cards

System przerwań mikrokontrolera ATmega32

Przerwania programowe: linie INT0, INT1 mogą być wyzwalane zboczem narastającym, zboczem opadającym, poziomem 0 oraz zmianą sygnału na przeciwny.

22

New cards

Mikrokontrolery rodziny AVR zbudowany jest w oparciu o model pamięci:

Równoległy (Harvard)

23

New cards

Obsługa timerów w mikrokontrolerach AVR. Sygnalizacja zdarzeń:

Timer Overflow (przepełnienie timera). Ustawienie tego bitu informuje, że timer osiągnął wartość maksymalną i zostanie wyzerowany w następnym cyklu zegarowym. Przepełnienie sygnalizowane jest przy pomocy bitu TOVx w rejestrze TIFR.

24

New cards

Metody synchronizacji potoku w procesorach CISC polegają na:

Stosowania dodatkowych szyn obejściowych spełniających rolę bufora danych

25

New cards

Instrukcja sterująca if (\~PIND & _BV(4)){...}; realizuje zadanie:

Testuj i zeruj bit 4

26

New cards

Cykl rozkazowy procesora jest ciągiem czynności wykonawcy przez CPU w celu wykonania jednej instrukcji przez procesor. Cykl rozkazowy procesora CISC na przykładzie x86 składa się:

Faza FETCH - pobranie instrukcji, w której wystawiany jest adres z PC do pamięci (CODE) przez bufor MBR

27

New cards

Procesory CISC charakteryzują się Architektura RISC

Duża liczba rozkazów prostych oraz niewielka złożonych

28

New cards

Architektura RISC cechuję się:

Prostym trybem adresowania pamięci - uproszczone odwołania do pamięci: tryby load i write

29

New cards

Co to jest akumulator i jaką pełni funkcje w strukturze mikroprocesora. Daj przykład wykorzystania A w operacji arytmetycznych na przykładzie mikrokontrolera 80C51

Akumulator wykorzystywany jest w operacjach arytmetyczno-logicznych w oparciu o zasoby CPU i pamięci wbudowanej. ADDC A,R1 - instrukcja dodaje zawartość A i zawartość R1 używając wskaźnika przeniesienia i umieszcza rezultat w A.

30

New cards

Jednostka obliczeń zmiennoprzecinkowych to

FPU

31

New cards

Mikrooperacja to:

Elementarna czynność układu sekwencyjnego, którą układ ten może zrealizować bez potrzeby rozkładania na czynności prostsze.

32

New cards

Procesor i486 zbudowany jest w oparciu o model pamięci:

Szeregowy (Von Neumann)

33

New cards

Jaki będzie wynik operacji odejmowania dwóch liczb heksadecymalnych : #003Bh - 0010h?

2Ah

34

New cards

Jakie podstawowe funkcje pełni rejestr flagowy

Rejestr flagowy zawiera flagi kontrolne i flagi sterujące pracą procesora określające tryb pracy oraz efekt wykonywania operacji przez procesor

35

New cards

Jakie podstawowe funkcje pełni rejestr PC

W zależności od modelu procesora w rejestrze tym przechowywany jest adres aktualnie wykonywanej lub następnej instrukcji

36

New cards

Na czym polega zasada odejmowania i dodawania w kodzie uzupełnienia do 2. Odejmowanie dwóch liczb dodatnich (A-B) o jednakowej podstawie można realizować przez dodanie do odjemnej p-tego uzupełnienia odjemnika, przy czym:

Jeżeli wystąpi przeniesienie z pozycji najbardziej znaczącej, to należy go odrzucić

37

New cards

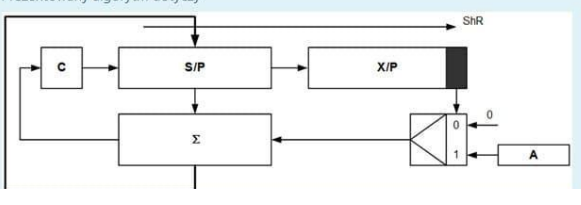

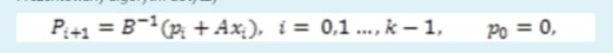

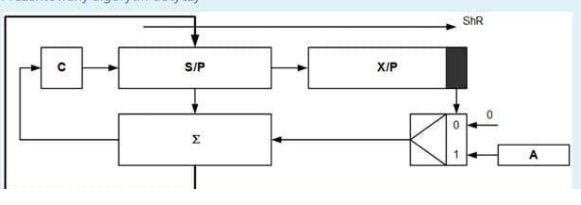

Prezentowany algorytm dotyczy:

Algorytm mnożenia akumulacyjnego w naturalnym systemie dwójkowym

38

New cards

Praca i486 w trybie rzeczywisty:

Pamięć podzielona jest na stałej długości segmenty po 64k; segmenty mogą na siebie zachodzić; fizyczna komórka pamięci może posiadać różne adresy logiczne.

39

New cards

Cechą/ funkcją rejestru rozkazu jest:

Jest wskaźnikiem do pamięci programu wskazujący kolejny rozkaz do wykonywania

40

New cards

Liczba 10011001100 zapisana w postaci heksadecymalnej ma postać

4CC

41

New cards

Prezentowany algorytm dotyczy

Algorytmem operacji mnożenia arytmetycznego z akumulacją z normalizacją

42

New cards

Prezentowany na rysunku procesor:

to procesor RISC zbudowany w architekturze równoległej (Harvard)

43

New cards

Kod BCD stosujemy do reprezentacji liczb:

W których cyfry dziesiętne są przedstawiane w kodzie dwójkowym

44

New cards

Dodatkowe cechy wyniku operacji wykonywanej przez jednostkę arytmetyczno - logiczną ALU:

Rejestr flagowy

45

New cards

Struktura pamięci - AVR na przykładzie układu ATmega 16:

Pamięć programu posiada organizację 8Kx16, adresowana jest przez 13-bitowy licznik rozkazów

46

New cards

Jednostka centralna CPU mikrokontrolera ATmega32 to:

Procesor RISC zbudowany w architekturze równoległej (zmodyfikowany Harvard)

47

New cards

Przerwanie od linii INTO wyzwalanej zboczem opadającym wymaga konfiguracji:

tmp = MCUCR; tmp |= 1 << ISC00; tmp |= 1 << ISC01; MCUCR = tmp; GICR |= 1 << INT0

48

New cards

Mikrokontroler AT91SAM7 z rdzeniem ARM7 to:

procesor RISC zbudowany w architekturze szeregowej (von Neumann)

49

New cards

Blok rejestrów pomocniczych ARx procesora TMS32C50 służy do:

Adresowania pośredniego wewnętrznej pamięci danych

50

New cards

Przedstawiony model pamięci dotyczy:

mikrokontrolery ARM Cortex-M4

51

New cards

Procesory sygnałowe posiadają kilka cech (niespotykanych w innych procesorach), zapewniających wysoką wydajność:

równoległe mnożenie z akumulacją, wykonywane w jednym cyklu pozwalające na realizację różnych operacji, np.: splotu

52

New cards

Przedstawione na rys. przebiegi czasowe:

Cykl zapisu do pamięci dynamicznej

53

New cards

Przerwania maskowalne sprzętowe są zgłaszane przez układy wewnętrzne mikrokontrolera do systemu przerwań. Przerwaniami maskowalnymi nie są:

Reset systemu, dzielenie przez zero, błędny kod rozkazu

54

New cards

Ścieżka danych procesora VLIW danych odpowiada za wykonywanie faktycznych obliczeń. Na przykładzie procesora DSP ścieżka danych zawiera:

ACC, rejestr skalujący, mnożarkę równoległą oraz pamięć wbudowaną

55

New cards

Jednostka centralna ARM 7:

Podwójny bufor magistrali adresowej umożliwiający schemat dostępu do pamięci Read-Modify-Write

56

New cards

Wektor przerwań to:

tablica zawierająca adresy źródeł przerwań sprzętowych oraz programowych

57

New cards

WAR (write after read) - INSTR:

Antidependence

58

New cards

Sytuacja gdy dochodzi do konfliktu w czasie dostępu do lokalizacji operandu. Dwie instrukcje zostaną wykonywane kolejno po sobie i obie odwołują się do konkretnej lokalizacji w pamięci lub rejestru operandu:

Data hazards

59

New cards

Jednostka centralna procesowa DSP TMS320C50 składa się – wskaż __**niepoprawną**__ odpowiedź:

Bloku rejestrów ogólnego przeznaczenia AX, BX, CX, DX

60

New cards

System przerwań procesora DSP posiada następujące cechy:

Nie obsługuje przerwań zanurzonych..

61

New cards

Prawo Amdahl’s mówi o:

wzrost wydajności zależy od szybszego trybu pracy i ograniczony jest czasem…

62

New cards

Cykl rozkazowy procesora jest ciągiem czynności wykonywany przez CPU w celu wykonywania jednej instrukcji przez procesor. Cykł rozkazowy procesora CISC na przykładzie x86 składa się:

Faza EXECUTE wykonanie operacji arytmetycznej lub logicznej...

63

New cards

Blok rejestrów pomocniczych Arx procesora TMS32C50 służy do

Adresowania pośredniego wewnętrznej pamięci danych

64

New cards

Mikrokontroler AT91SAM7 z rdzeniem ARM7 to:

procesor RISC zbudowany w architekturze szeregowej (Von Neumann)

65

New cards

Rdzeń ARM7 posiada podobnie jak procesor DSP przesuwnik bitowy, który realizuje-wskaż __**błędną**__ odpowiedź:

Służy do skalowania obu argumentów w rozkazach arytmetycznych i logicznych

66

New cards

Wynik operacji zgodnej z arytmetyką stałoprzecinkową Z=X\*Y(-0,5 Q15 0,5 Q15), wyniesie w zapisie Q15:

**01**000000000000

67

New cards

Przerwania maskowalne sprzętowe są zgłaszane przez układy wewnętrzne mikrokontrolera do systemu przerwań. Przerwaniami maskowalnymi __**nie są**__:

Reset systemu, dzielenie przez zero, błedny kod rozkazu

68

New cards

Praca i486 w trybie rzeczywisty:

Pamięć podzielona jest na stałej długości segmenty po 64k; segmenty mogą na siebie zachodzić; fizyczna komórka pamięci może posiadać różne adresy logiczne

69

New cards

Rejestry selektorów procesora i486 służą do:

Wskazuje deskryptor z adresem bazowym w trybie chronionym

70

New cards

Przedstawiony na rys. przebiegi czasowe dotyczą

cykl __**ZAPISU**__ do pamięci dynamicznej

71

New cards

Procesory sygnałowe posiadają kilka cech(niespotykanych w innych procesorach), zapewniających wysoką wydajność:

Równoległe mnożenie z akumulacją, wykonywane w jednym cyklu pozwalające na realizację różnych operacji, np.:splotu

72

New cards

Blok rejestrów pomocniczych ARx procesora TMS32C50 służy do:

Adresowania pośredniego wewnętrznej pamięci danych

73

New cards

Przedstawione na rys. przebiegi czasowe dotyczą:

cyklu __**ODCZYTU**__ z pamięci statycznej SRAM

74

New cards

Jednostka specjalna procesora DSP TMS320C50 składa się - wskaż __**niepoprawną**__ odpowiedź:

Bloku rejestrów ogólnego przeznaczenia **AX,BX,CX,DX**

75

New cards

System przerwań procesora DSP posiada następujące cechy:

Nie obsługuje przerwań zanurzonych, rejestry pamiętane są na stosie 1-poziomowym

76

New cards

Procesor ARM7 posiada następujące cechy - wskaż poprawną odpowiedź:

Obsługuje następujące wyjątki: **IRQ,FIQ,ABORT,UNDEFINED,SWI**, które są nadrzędne wzg. programu głównego

77

New cards

Ścieżka danych procesora VLIM danych odpowiada za wykonanie faktycznych obliczeń. Na przykładzie procesora DSP ścieżka danych zawiera:

Moduły **L,S,M,D**

ACC, rejestr skalujący, mnożarkę równoległą oraz pamięć wbudowaną

ACC, rejestr skalujący, mnożarkę równoległą oraz pamięć wbudowaną

78

New cards

Wektor przerwań to:

**Tablica** zawierająca **adresy źródeł przerwań** sprzętowych oraz programowych

79

New cards

Cykl rozkazowy procesora jest ciągiem czynności wykonywanych przez CPU w celu wykonywania jednej instrukcji przez procsor. Cykl rozkazowy procesora **CISC** na przykładzie **x86** składa się:

Faza **FETCH** - pobranie instrukcji, w której wystawiany jest **adres PC** do pamięci **(CODE)** przez bufor **MBR**

80

New cards

Metody **synchronizacji potoku** w procesorach **CISC** polegają na:

Wykonywaniu **wielu rozgałęzień** programu do czasu sprawdzenia warunku rozgałęzienia

Stosowania **dodatkowych szyn obejściowych** spełniających rolę bufora danych

**Grupowaniu instrukcji** i oznaczaniu ich wzajemnych relacji już na etapie kompilacji programu

Stosowania **dodatkowych szyn obejściowych** spełniających rolę bufora danych

**Grupowaniu instrukcji** i oznaczaniu ich wzajemnych relacji już na etapie kompilacji programu

81

New cards

Prawo Amdahl’s mówi o:

Wzrost wydajności zależy od **szybszego trybu pracy** i **ograniczony jest czasem używania** takiego trybu pracy

82

New cards

Sytuacja, gdy dochodzi do konfliktu w czasie dostępu do lokalizacji operandu. Dwie instrukcje zostaną wykonywane kolejno po sobie i obie odwołują się do konkretnej lokalizacji w pamięci lub rejestru operandu:

**Data hazards**

83

New cards

WAR( write after read) - INSTRb próbuje zapisu do lokalizacji docelowej zanim INSTRa odczyta z tej lokalizacji, INSTRa niepoprawnie odczytuje nową wartość. Hazard ten jest wynikiem :

Antidependence

84

New cards

Przedstawiony model pamięci dotyczy

Mikrokontrolera ARM Cortex-M4

85

New cards

Jednostka centralna ARM7:

**Podwójny bufor** magistrali adresowej umożliwiający schemat dostępu do pamięci **Read-Modify-Write**

86

New cards

System **przerwań** mikrokontrolera ATmega32:

Przerwania programowe INT0, INT1 mogą być wyzwalane zboczem __**narastającym**__, zboczem __**opadającym**__, __**poziomem 0**__ oraz __**zmianą sygnału na przeciwny**__

87

New cards

**Mikrokontrolery** rodziny __**AVR**__ zbudowane są w oparciu o model pamięci:

**Równoległy(Harvard)**

88

New cards

Obsługa timerów w mikrokontrolerach AVR. Sygnalizacja zdarzeń:

__**Timer Overflow**__(przepełnienie timera). Ustawienie tego bitu informuje, że **timer osiągnął wartość maksymalną** i zostanie wyzerowany w następnym cyklu zegarowym. Przepełnienie sygnalizowane jest przy pomocy bitu **TOVx** w rejestrze TIFR.

89

New cards

Instrukcja sterująca if(\~PIND & _BV(4)){…}; realizuje zadanie:

Testuj i zeruj bit 4

90

New cards

Procesory **CISC** charakteryzują się:

**dużą liczbą rozkazów prostych** i niewielką złożonych

91

New cards

Architektura __**RISC**__ cechuje się:

**Prostym** trybem **adresowania** pamięci - **uproszczone odwołania do pamięci**: tryby **load i write**.

92

New cards

Co to jest akumulator i jaką pełni funkcję w strukturze mikroprocesora. Daj przykład wykorzystania A w operacji arytmetycznej na przykładzie mikrokontrolera 80C51:

Akumulator wykorzystywany jest w operacjach arytmetyczno-logicznych w oparciu o zasoby CPU i pamięci wbudowanej. ADDC A, R1 - instrukcja dodaje zawartość A i zawartość R1 używając wskaźnika przeniesienia i umieszcza rezultat w A

93

New cards

Jednostka obliczeń zmiennoprzecinkowych to:

FPU

94

New cards

Mikrooperacja to:

Elementarna czynność układu sekwencyjnego, którą ten układ noże zrealizować bez potrzeby rozkładania na czynności prostsze

95

New cards

Procesor **i486** zbudowany jest w oparciu o model pamięci:

**Szeregowy** (Von Neumann)

96

New cards

Jaki będzie wynik operacji odejmowania dwóch liczb heksadecymalnych: #003Bh - 0010h?

2A(H)

97

New cards

Jakie podstawowe funkcje pełni rejestr flagowy?

Rejestr flagowy zawiera **flagi sterujące pracą procesora** określające **tryb pracy** oraz **efekt wykonywania operacji** przez procesor

98

New cards

Jakie podstawowe funkcje pełni **rejestr PC**?

W zależności od modelu procesora w rejestrze tym przechowywany jest **adres aktualnie wykonywanej lub następnej instrukcji**

99

New cards

Na czym polega **zasada odejmowania i dodawania** ?

Jeżeli wystąpi **przeniesienie z pozycji najbardziej znaczącej** to należy go **odrzucić**

100

New cards

Prezentowany algorytm dotyczy

Algorytm **mnożenia akumulacyjnego** w naturalnym **systemie dwójkowym**