OPERATING SYSTEMS

1/53

There's no tags or description

Looks like no tags are added yet.

Name | Mastery | Learn | Test | Matching | Spaced |

|---|

No study sessions yet.

54 Terms

Generations of computers

1st Gen: vacuum tubes; manual

2nd Gen: transistors & batch operating

3rd Gen: intergrated circuits & multiprog

4th Gen: PCs: GUI

5th Gen: mobile and cloud computing

OS systems

Windows, Linus, iOs, Android

Operating System/system software?

comp progs that administrate resources of a computer and make them available via interfaces

Goals of OS

abstraction of Hardware

Resource management

communication

security

What does OS do?

examine or alter any process’s memory

read, write, delete or corrupt any file on any writeable persistent

storage medium

change the scheduling or even halt execution of any process

send any message to anywhere, including altered versions of a process’s messages

enable, disable, or use any peripheral device

reliabilty?

protection against accidental/unintentional damage

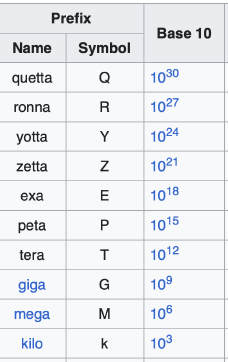

KB

KiB

Modes of operating system?

user mode(restricted) and kernel mode(priveleged)

in user mode, only the application crashes; in kernel mode, the whole system goes down

Process vs thread

A process is a running program while thread is a lightweight process.

process is needed to create multiprogramming systems

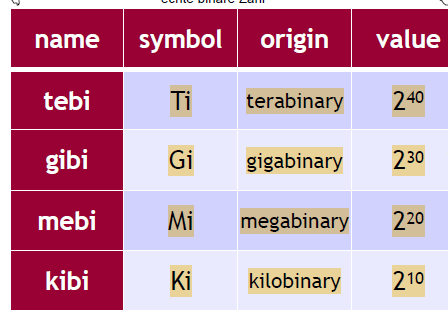

architecture of a computer

instruction cache why needed?

stores frequently used instructions;

advantage: faster retrival and execution

vNA, HA, mHA?

vNA: cannot read data and instructions at the same time

HA: can do what vNA cant; better performance but complexity

mHA: just like Harv Arch but has an instruction cache

Bus?

a set of parallel pathways for data and control signals;

The CPU, memory, and I/O devices are all connected by a system bus and communicate with one another over it. (in a PC)

Direct Memory Access

transfer data directly without interfering with the CPU;

HOLD (hold signal) and HLDA (hold acknowledge) to initiate process;

CPU receives interrupt oncecopying is done;

why CPU mit registers?

memory access is slow compared to execution of instructions

computer organization

the way a given instruction set architecture (ISA) is implemented in a particular processor

CPU has?

Program counter

Stack pointer

Flags indicate status

Fetch / Decode / Execute pipelines

multicore caching?

Hyper-Threading increases the number of instructions available to the superscalar pipeline by enabling two threads to issue instructions simultaneously on a single physical core. This enhances resource utilization by allowing multiple instructions from different threads to operate in parallel on separate data, improving overall throughput.

interrupts cause?

‣ Event-driven interruption of program flow;

short privileged subprogram executed by interrupt handler

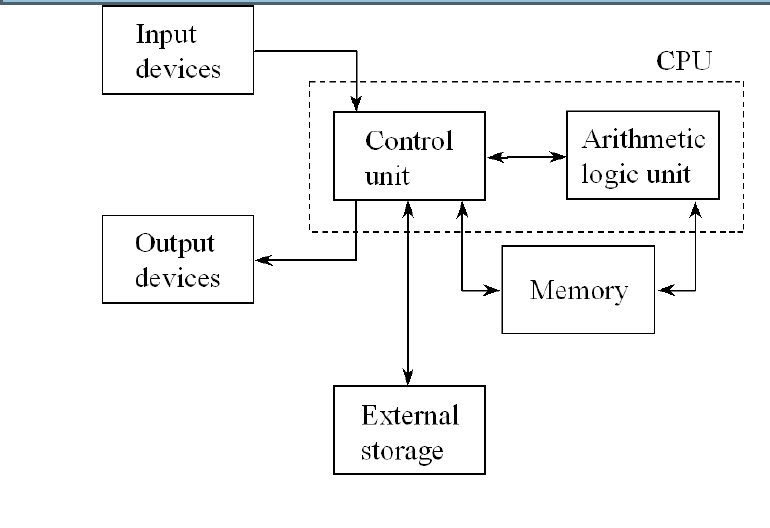

process states

process paralleity how?

pseudo-parallelism:

each process is run for a short time, about 10 to 100 ms each

Processes still run sequentially, but can be interrupted anytime

Also solves another problem: switching to time-critical tasks

process control block?

owned by eacj process

Unique process identifier (PID)

State

Complete execution state (program counter, stack pointer, registers)

Resources (memory, files, …)

Other information (scheduling, rights, …)

context switch ?

is switching CPU execution between different active processes.

the operating system

1. Stores the current process’ state in its process control block

2. Sets the system state to another process’ state from its control block

consequence sof process switching

‣ Exact timing of processes is non-deterministic

‣ Anything can happen between two CPU instructions

‣ Context switching consumes CPU time and happens often

Interrupt handler structure?

1. Save program state

2. Check/handle device activity (reason why we interrupted)

3. Restore program state

4. Continue interrupted program

Types of interrupts

hardware: asynchronous; occurs at arbitary times; generated by internal &external devices

software: synch; occurs at a specific point in the execution of the

CPU’s instructions; generated by instructions

interrupt controller n vector?

‣ interrupt controller: hardware component that manages and prioritizes interrupts from various sources

‣ interrupt vector: serves as a lookup table or array that maps interrupt numbers or codes to the memory addresses of their corresponding interrupt service routines (ISR)

Handling of external interrupts:

1. A device signals its interrupt via the bus.

2. The interrupt controller recognizes it.

3. The interrupt controller signals the CPU, providing a number identifying the device.

4. The CPU uses the number to retrieve the address of the interrupt service routine from the interrupt vector.

5. The CPU saves the current state.

6. The CPU calls the interrupt service routine.

7. The CPU restores the saved state.

8. The CPU signals the interrupt controller that the interrupt has been handled.

Interrupts within interrupts?

either forbidden or nested interrupts or interrupt priorities

Where is the interrupt vector stored?

either pointer/register or fixed memory address

Where is the current state stored?

registers need to be saved: e.g., single stack for all interrupts, some processors

have a complete second set of registers

diff betwen impreecise and precise interrupts

Precise interrupts: interrupted instruction is completed and architectural state (registers, program counter, etc.) reflects the state before the interrupt

Imprecise interrupts: allow some speculative execution or out-of-order execution when continuing after interrupt

Daemon

Background process

When are processes created?

‣ System initialization (init process PID 1)

‣ Other processes

‣ User

‣ Batch jobs

fork() work?

‣ Creates a new (child) process

‣ Child process is a copy of parent process

‣ Child has unique process identifier (PID)

‣ File descriptors are shared

‣ Return value indicates success (success: fork() returns 0 & PID of child to parent process; otherwise -1)

When are processes terminated?

‣ Regular termination (voluntary) exit(int status)

‣ Error (voluntary) signal

–––––––––––––––

‣ Severe error (by operating system)

‣ Other process (involuntary)

Process API:

set of system calls provided by an operating system to allow programs to interact with and control processes, e.g.: int kill(pid_t pid, int sig)

Thread

threads of a process share the same address space;

faster and use less memory as comparfed to processes

control of CPU execution

Thread switches

require fewer resources to be stored/retrieved:

‣ Unique thread identifier

‣ State (running, blocked, …)

‣ Complete execution state (program counter, stack pointer, registers)

‣ Resources: stack

Thread API

‣ Create a thread; accepts a callable (function)

‣ Exit from thread

‣ Join another thread, that is, block until it finishes

‣ Yield execution: volunteer to not being scheduled for now

POSIX threads(pthreads):

‣ pthread_create (similar to fork), pthread_exit, pthread_join,

pthread_yield

‣ pthread_attr_init, pthread_attr_destroy

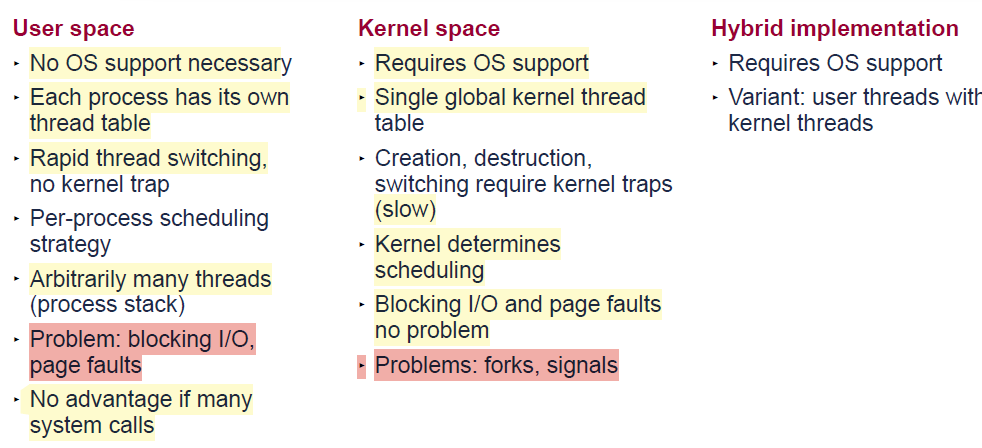

Thread implementation

Scheduling?

The scheduler decides which process to run next using a scheduling algorithm

Different scenarios require different strategies/algorithms

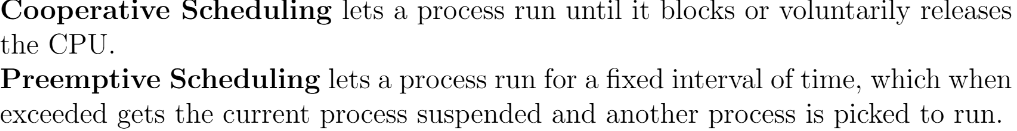

cooperative vs preemptive scheduling

coop: embedded systems

preeemptive: modern OS; timer interupts

Scheduling scenarios

Batch processing

Structured processing of non-interactive tasks

Mainframes, data centers

Bulk database updates, automated transaction processing, scientific computing, …

Interactive systems

Few interactive tasks

Personal computers, servers

Office software, programming, email, …

Real-time systems

Known time-constrained tasks

Devices (measurement, control, processing)

Embedded/industrial/ medical devices, robots, video/audio, …

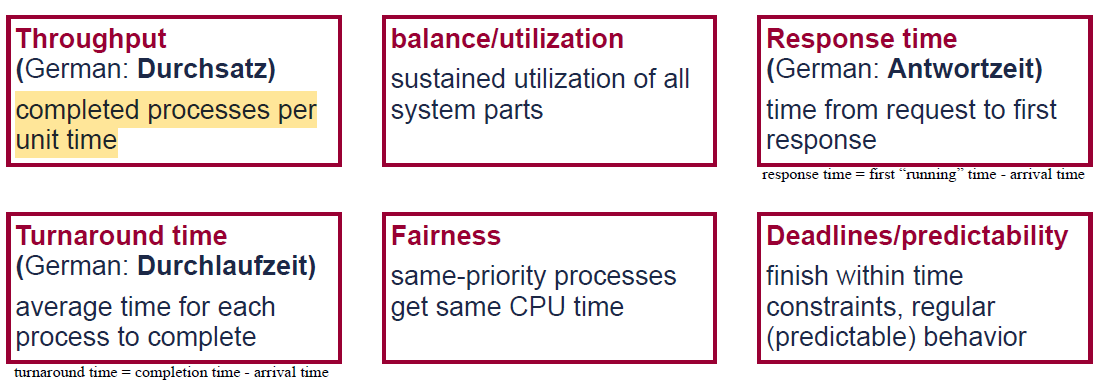

scheduling criteria

Separation of scheduling algorithm and policy via parametrization

enables processes and users to influence the schedule

First Come First Serve

jobs processed in order of arrival

cooperative scheduling

implementation in queue

can be ineff

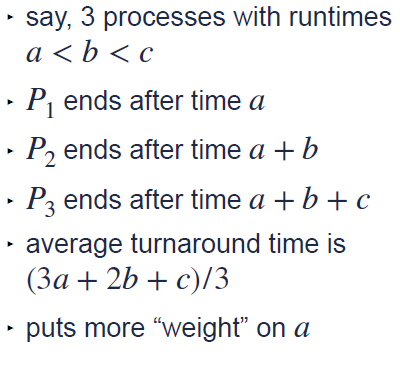

shortest job first

‣ Jobs are processed in order of their runtimes

‣ Cooperative form of scheduling

‣ Provably shortest turnaround times

vulnerable; starvation

shortest remaining time next

Jobs are processed in order of their remaining runtimes

Preemptive variant of Shortest-Job First scheduling

Round Robin

‣ Each process can run at most for a given time quantum

(time slice)

‣ Preemptive form of scheduling

‣ Assumes all processes are equally important

‣ Another process is switched in if the current process either

(a) blocks due to I/O or

(b) exceeds its time quantum

+ Prevents starvation

− Bad turnaround times, no priorities

Priority scheduling

Schedule processes with higher priority first

‣ Preemptive form of scheduling

‣ Priorities can be dynamically adjusted,

-starvation: ‣ Hybrid variant:

Priority classes, round-robin scheduling within class (still starvation)

Lottery scheduling

‣ Stochastic scheduling, resources assigned via lots

‣ Preemptive form of scheduling

‣ Priorities via additional lots

Multi-Level Feedback-Queue scheduling

‣ Optimize turnaround time and response time for users (generally contradictory objectives)

‣ Preemptive form of scheduling

‣ Hybrid between priority and Round-Robin scheduling (within same priority)

‣ Varies priorities based on observed behavior: processes that consumed their CPU quantum are de-prioritized

‣ Starvation (fixed by boosting)

‣ Can be gamed