PPI

1/89

There's no tags or description

Looks like no tags are added yet.

Name | Mastery | Learn | Test | Matching | Spaced | Call with Kai |

|---|

No analytics yet

Send a link to your students to track their progress

90 Terms

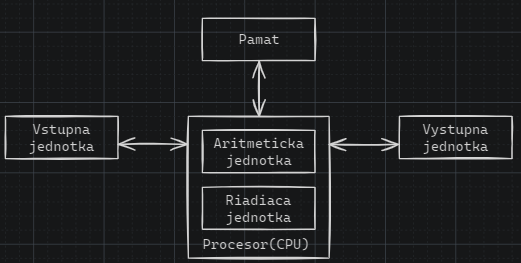

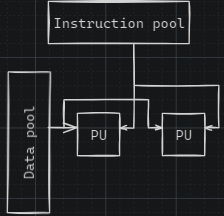

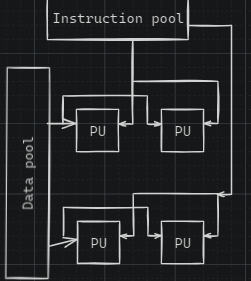

Princetonska architektura

Pocitacovy system v sucasnosti

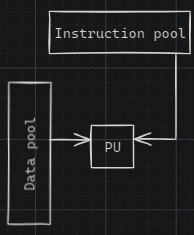

Flynnova klasifikacia SISD

- seriovy pocitac, jednoprocesorovy

- je predstavitelom von Neumanovskej architektury

- Starsie PC, mainframe

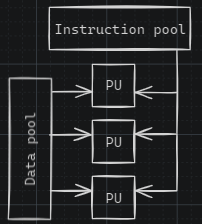

Flynnova klasifikacia SIMD

- viacprocesorovy, paralelny pocitac (maticovy)

- vypocty na grafickych kartach

Flynnova klasifikacia MISD

- viacprocesorovy pocitac (prudove spracovanie)

- vysoky stupen spolahlivosti

Flynnova klasifikacia MIMD

- viacprocesorovy, paralelny pocitac

- distributovane pocitace

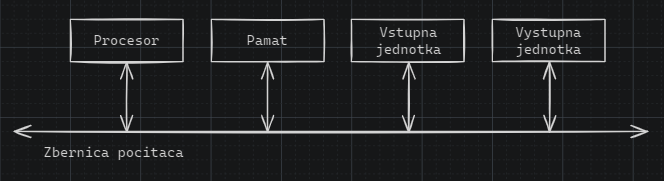

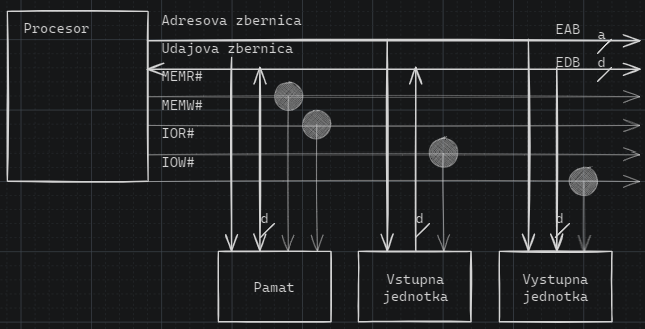

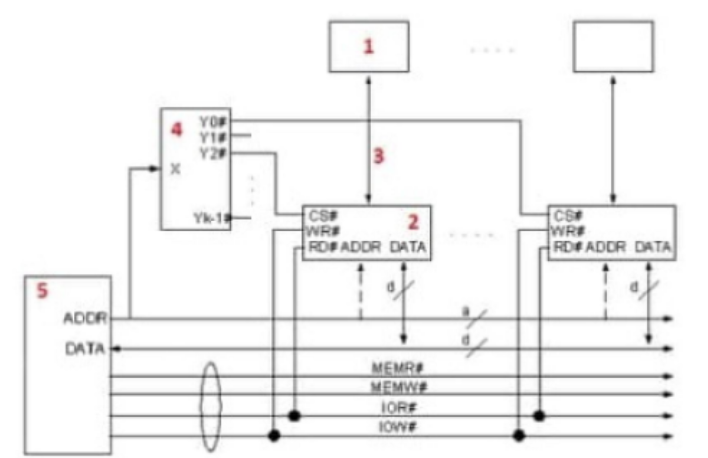

Typicka systemova zbernica SINGLE MASTER

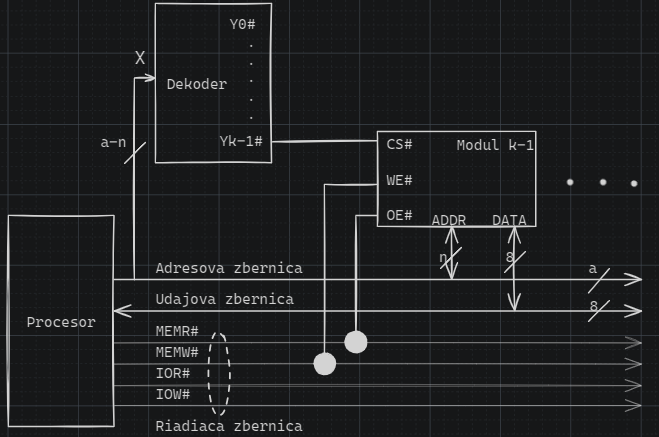

Pripojenie k zbernici pocitaca pamatovych obvodov (modulov)

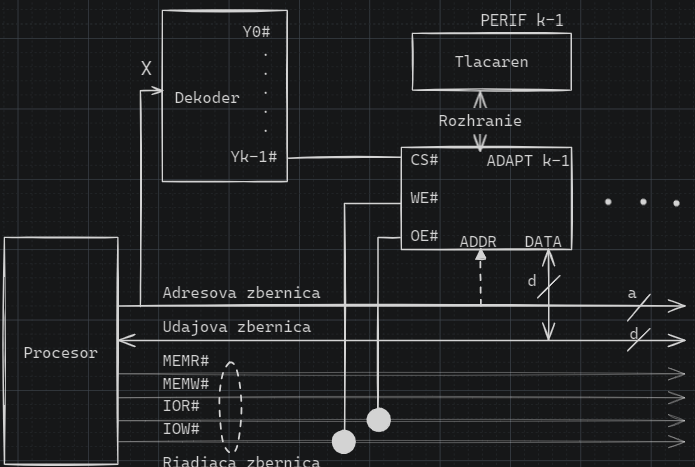

Pripojenie k zbernici pocitaca PERIFerijnych zaradeni

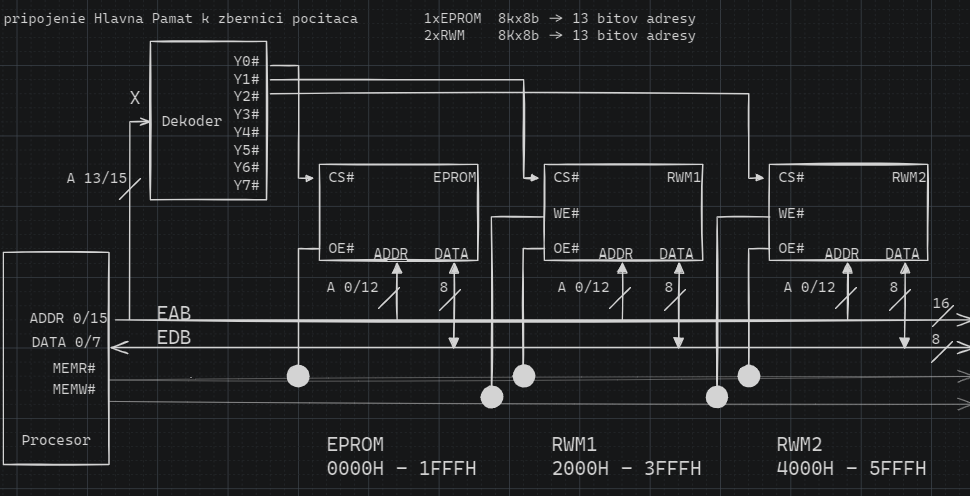

Pripojenie Hlavna Pamat k zbernici pocitaca

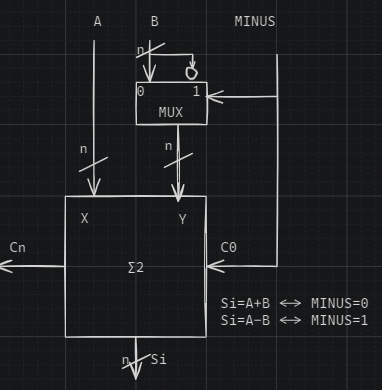

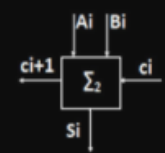

N-bitova binarna scitacka/odcitacka

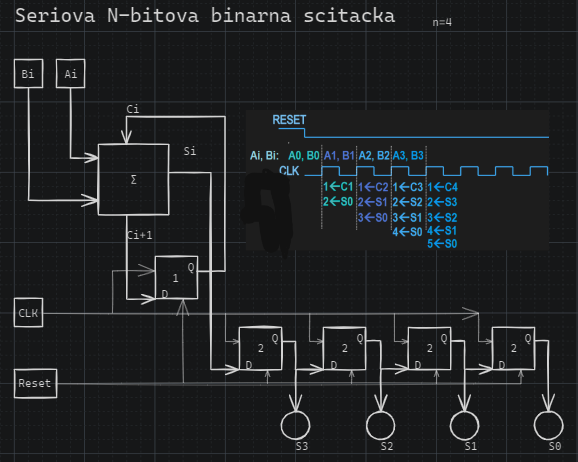

Seriova N-bitova binarna scitacka

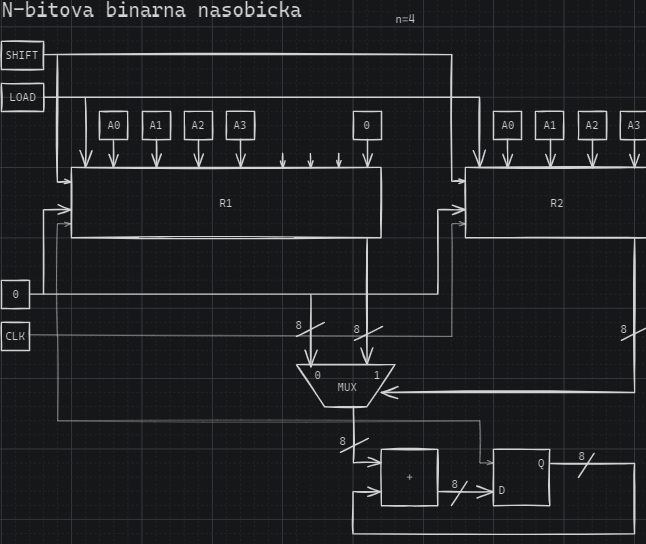

N-bitova binarna nasobicka

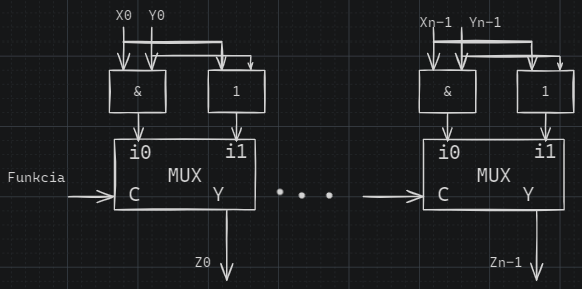

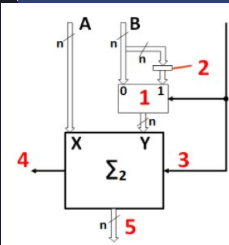

Viacfunkcna funkcna jednotka

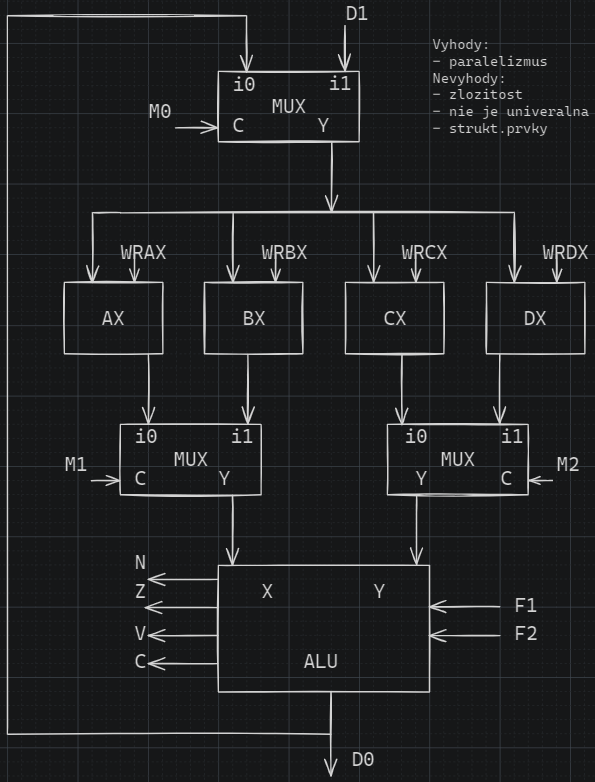

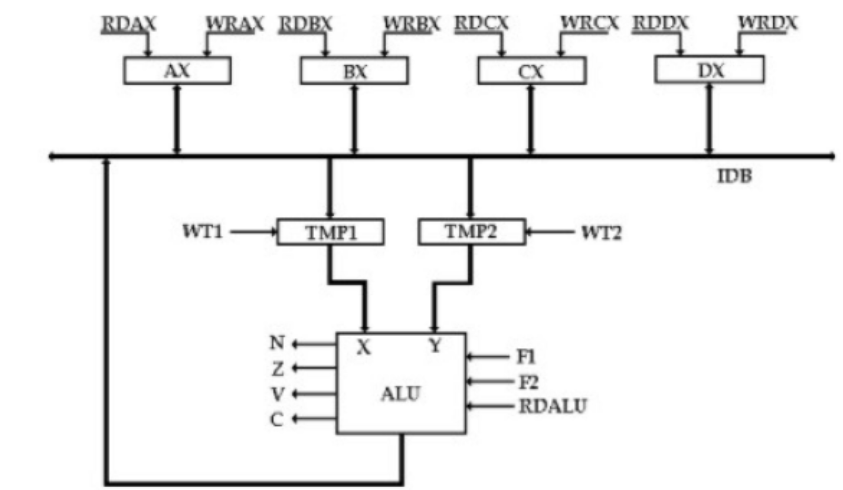

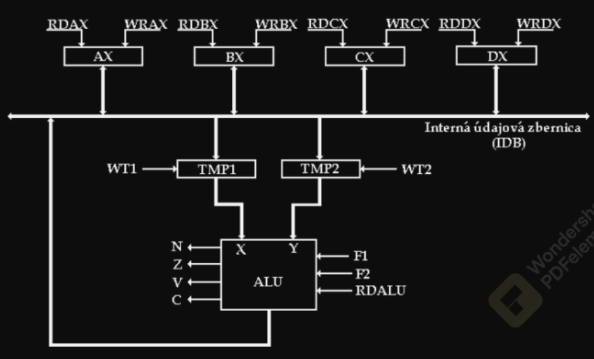

Pripojenie registrov s ALU prostrednictvom multiplexorov a demultiplexorov

+ paralelizmus

- zlozitost

- nie je univeralna

- strukt. prvky

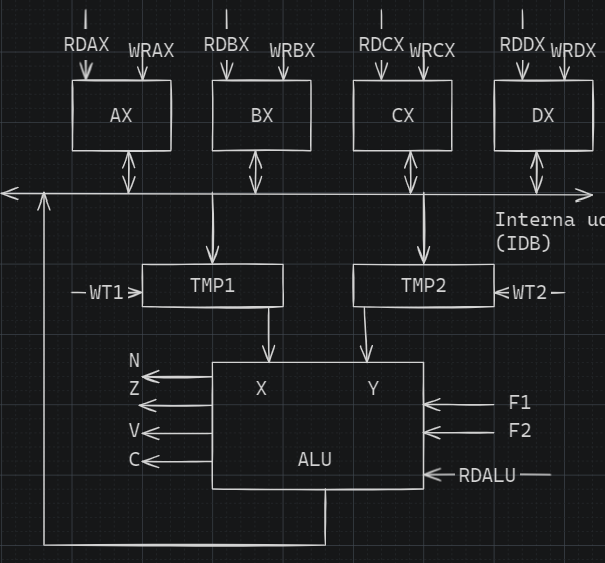

Pripojenie registrov s ALU prostrednictvom zbernice

+ univerzalnost

+ jednoduchost

- non paralelizmus

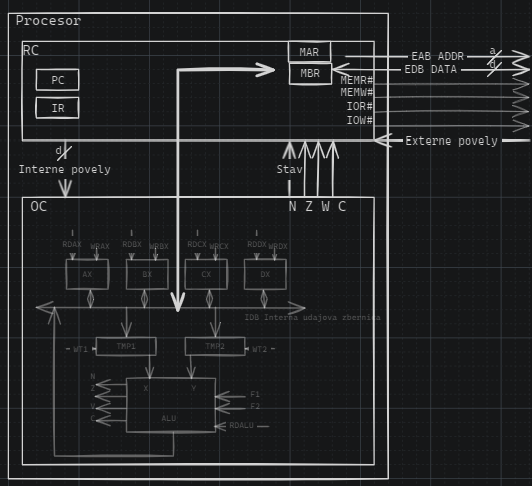

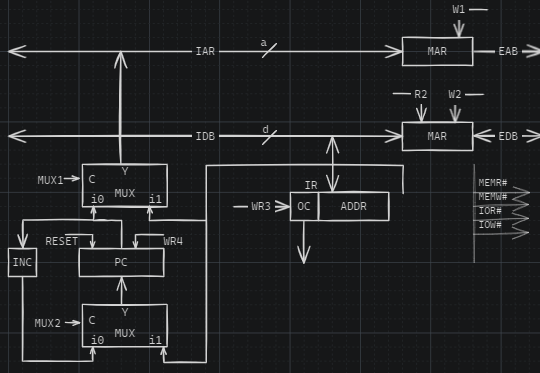

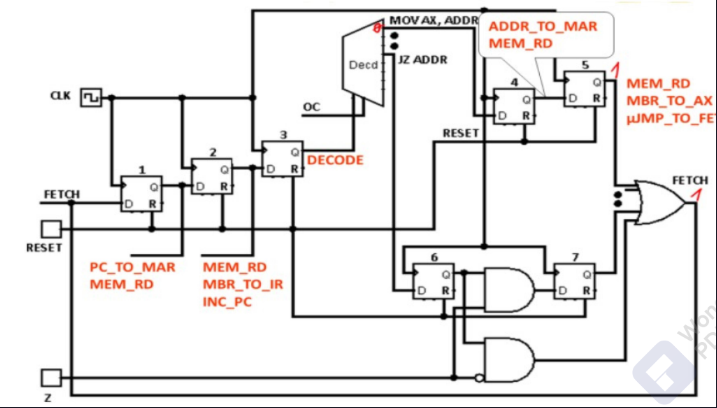

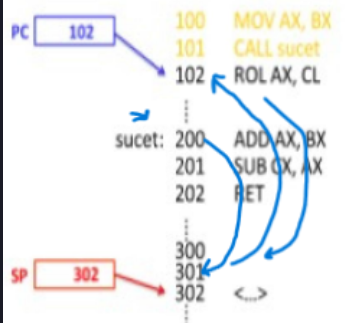

Navrh RC procesora - prepojenie OC s RC

Riadiaca cast - pripojenie na externu zbernicu

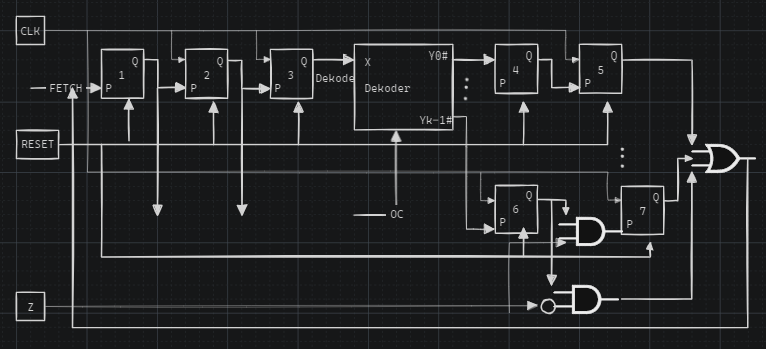

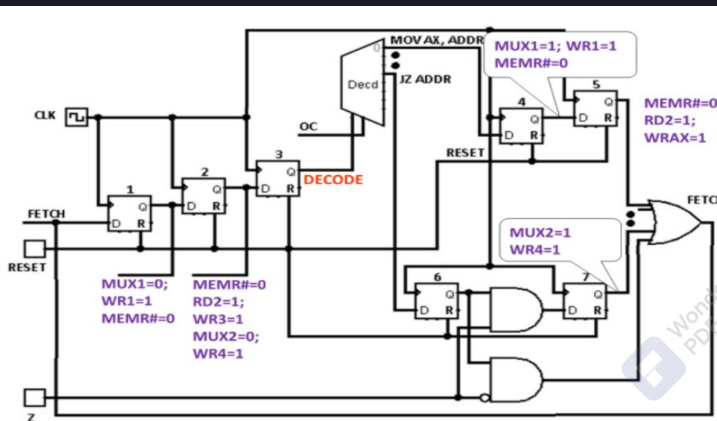

Riadiaca cast s pevnou logikou

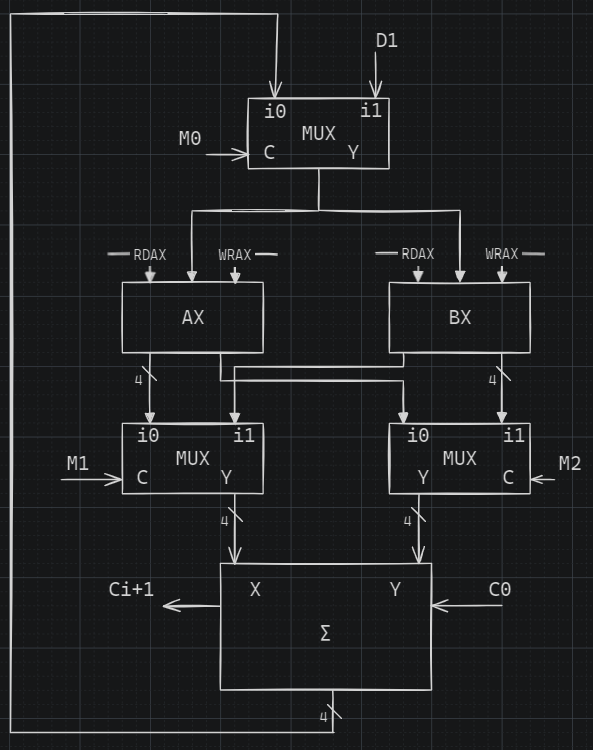

Pomocou multiplexorov a demultiplexorov navrhnite blokovú schému jednoduchej operačnej časti, ktorá obsahuje 4-bitovu sčítačku/odčitačku a dva 4-bitove registre. Výstup každého z registrov sa dá pripojiť na ľubovoľný z údajových vstupov sčítačky/odčítačky. Do každého registra sa dá zapísať výstup zo sčítačky/odčítačky alebo externy vstup.

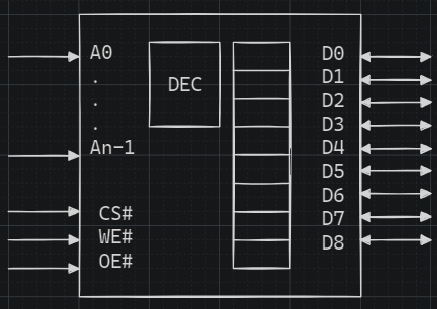

Hlavna pamat pocitaca - RWM

Staticke (RWM) - kazda bunka je realiz. PO

Organizacia - obycajne slabikova -> 8 bitovu ud. zb.

- lokova schema RWM - staticka s organizaciou 2^n x 8

- DEC 1 z 2^n pamatovych buniek

- A 0/n-1 - adresove vstupy

- sluzia na vyber konkr. bunky M

- D 0/7 - obojesmerne udajove vsupy / vystupy

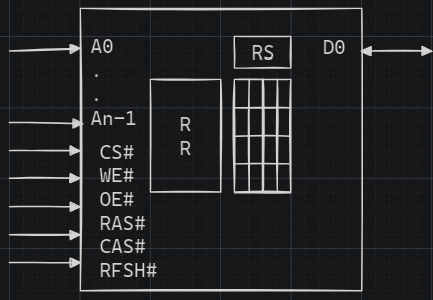

Hlavna pamat pocitaca - DRAM

Dynamicke (DRAM) je rganizovany ako tabulka

Typicka organizacia: 2^n x (1|4) bit

- 2 pomocne registre

- na adr. riadku - RAS#

- nd adr. stlpca - CAS#

- RFSH# - refresh

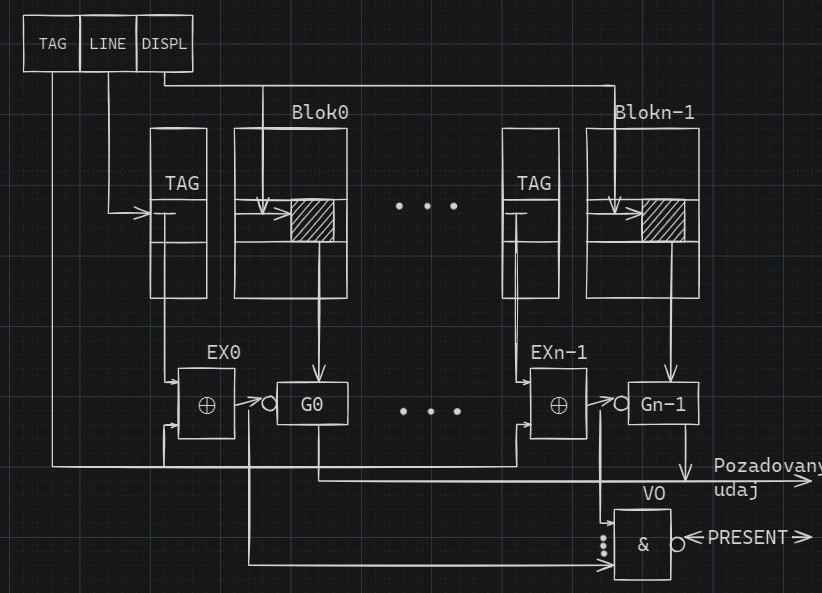

Vyrovnacia pamat z mnozinou blokov

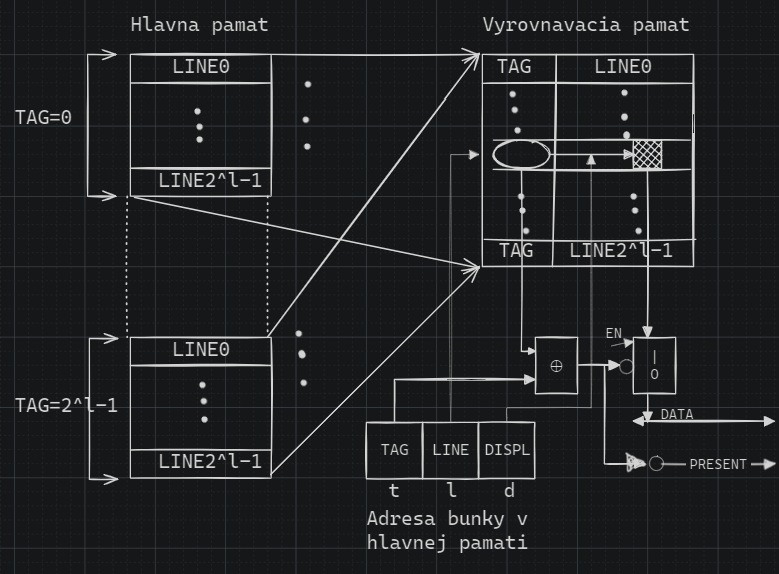

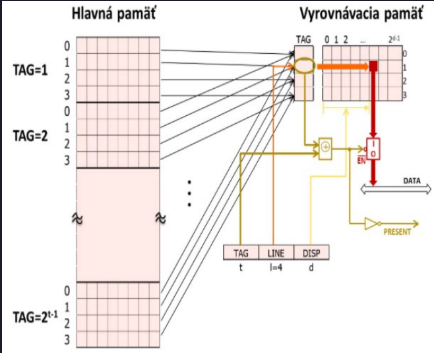

Model vyrovnavacej pamati s priamym mapovanim

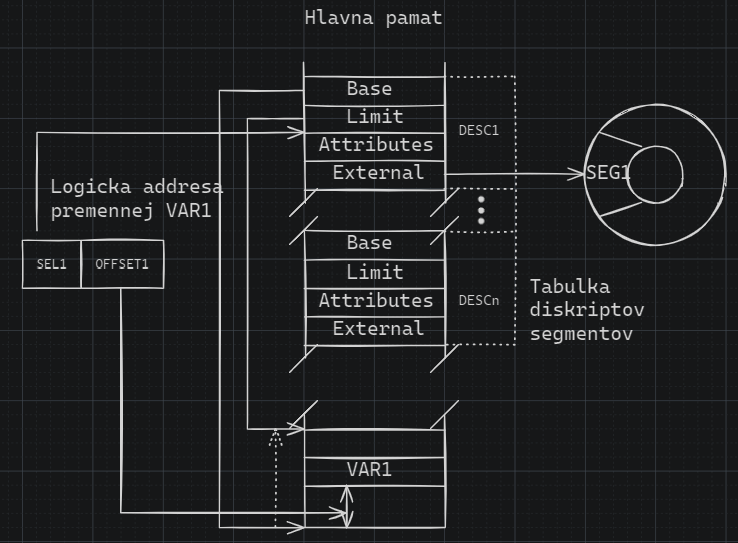

Segmentacia

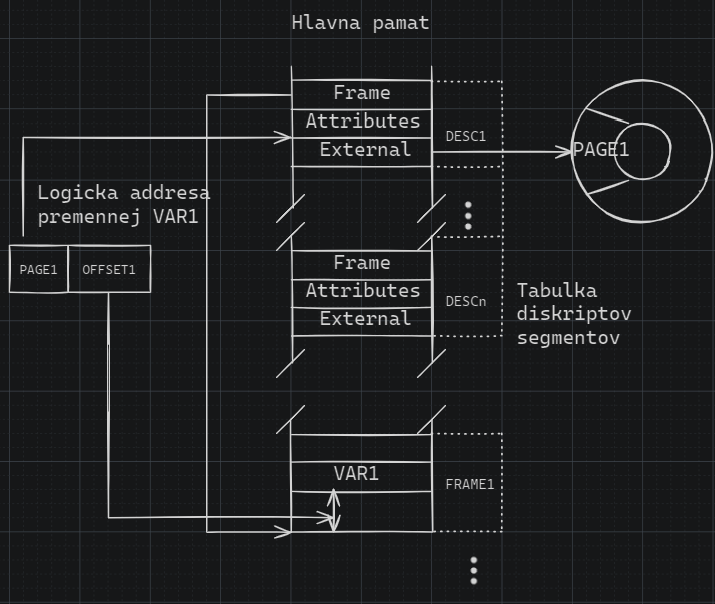

Strankovanie

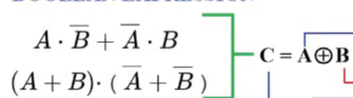

multiplexor | n-bitovy negator | C0 | Cn | S

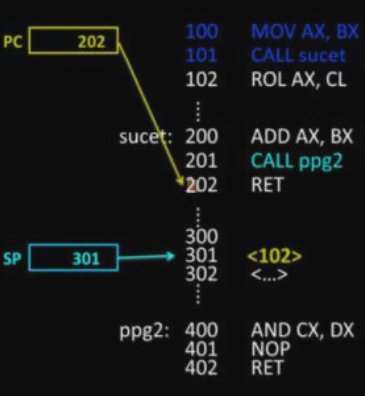

Uvažujte fragment …1 s ....2

Koľko taktov sa bude vykonávať inštrukčný cyklus pre inštrukciu

MOV AX, ADDR ...3?

JS ADDR … 4 v prípade, že príznak …5 nie je nastavený (má hodnotu 0)?

riadacejjednotkypevnoulogikou5

4

ZERO

200 , 301, 102, 301

Aktivita na úrovni medzi registrových prenosov, ktorej realizáciu predpisuje ...1 DXtoTMPl (3), ALUtoAX (4), je ...2, iniciovaná nastavením riadiacich signálov:

- ...

- ...

- ...

microinstrukciamikrooperaciaRDDX,WT1RDALU, WRAX

Obrázok reprezentuje model vyrovnávacej pamäti s ... ... ....1

Hlavná nevýhoda tohto modelu je, že vo vyrovnávacej pamäti sa nemôže súčasne nachádzať ... ... ...2

Ďalšie používané modely sú:

vyrovnávacia pamäť s ... ... ... 3 a ... ....4

priamymmapovanimrovnakyriadokmnozinoublokovplneasociativna

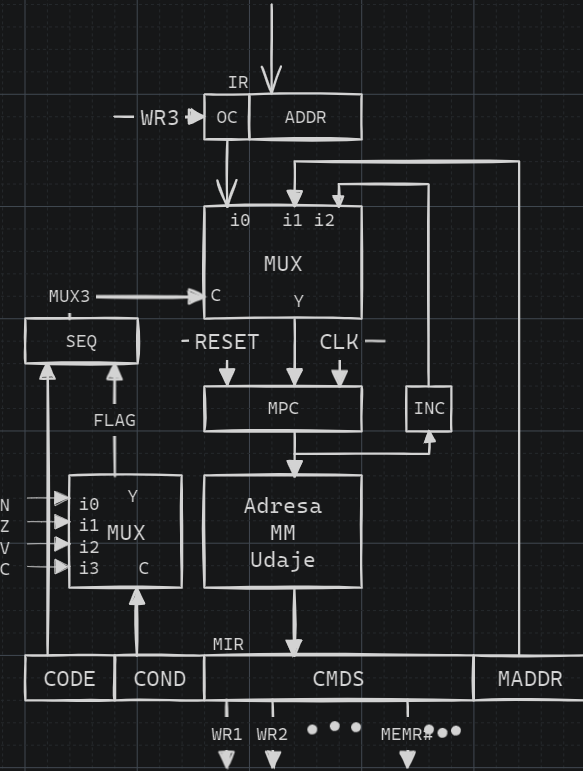

Fragment ...1 s ... ..2.

Ako by ste realizovali boolovskú funkciu pre riadiaci signál

MEMR#(3)?

WR4# (4) ?

- ... ... typu ...

na ktorého vstup sa pripoja výstupy preklápacích obvodov číslo:

...

...

riadiacej

jednotkypevnou logikoulogickym clenom,NOR(1,2,4,5)

logickym clenom, OR

(2, 7)

1. periferne zariadenie

2. adapter

3. rozhranie

4. decoder

5. procesor

Čo musí zabezpecit obslužný program prerušenia na začiatku a na konci obsluhy prerušenia?

odloženie stavu procesora a obnovenie povodneho stavu procesora

Koncepcia von Neumannovho počítača je charakteristická týmito vlastnostami:

procesor vyberie z pamati takú inštrukciu, na ktorú ukazuje programové počítadlo • inštrukcie sa vykonávajú podlá poradia ako su ulozene v pamati, pokial sa nevykoná inštrukcia skoku.

Prúdové spracovanie inštrukcii ma oproti neprudovemu spracovaniu tieto vyhody (predpokladáme ten istý inštrukčný súbor):

vykonnost prostriedkov s prúdovým spracovaní inštrukcii Je vyššia.

Rozšírenie operačného kódu znamená, že pri vybranej hodnote operačného kódu sa pole operačného kódu predĺži

Register IR obsahuje práve vykonávanú inštrukciu

Register PC obsahuje počet vykonaných inštrukcií

ALU slúži na vykonávanie aritmeticko-logických operácií a na zapisovanie údajov do pamäte.

Rozšírenie operačného kódu znamená, že v každej inštrukcii bude pole operačného kódu rozšírené na úkor poľa adresy

Každý formát inštrukcie obsahuje pole operandu

Multiplexor sa používa na prepínanie údajových ciest v operačnej časti s kanálovou architektúrou

true

true

false

false

false

false

true

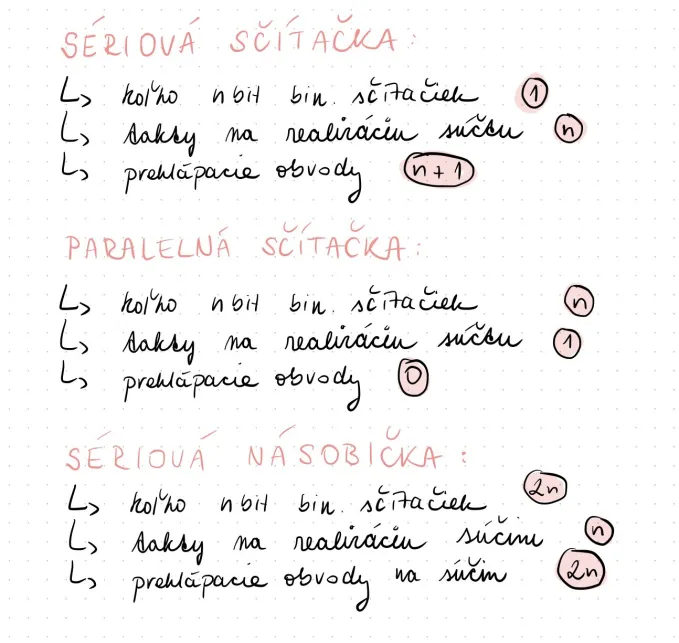

Koľko jednobitových binárnych sčítačiek je potrebných na realizáciu n-bitovej sériovej násobičky?

2n

Koľko jednobitových binárnych sčítačiek je potrebných na realizáciu n-bitovej sériovej sčítačky?

1

Koľko jednobitových binárnych sčítačiek je potrebných na realizáciu n-bitovej paralelnej sčítačky?

n

Koľko preklápacích obvodov je potrebných na realizáciu n-bitovej paralelnej sčítačky?

0

Kolko preklápacích obvodov je potrebných na realizáciu n-bitovej sériovej sčítačky?

n+1

Koľko preklápacích obvodov je potrebných na uchovanie súčinu dvoch n-bitových operandov pomocou n-bitovej sériovej násobičky?

2n

Koľko taktov je potrebných na realizáciu súčtu dvoch nbitových operandov pomocou n-bitovej sériovej sčítačky?

n

Koľko taktov je potrebných na realizáciu súčtu dvoch nbitových operandov pomocou n-bitovej paralel. sčítačky?

1

Fyzický adresový priestor počítača je spravidla:

menší ako logický adresový priestor

Virtuálna pamäť počítača je daná:

logickou adresou

Fyzický adresový priestor počítača je daný:

absolútnou adresou

Prúdové spracovanie inštrukcie je charakteristické tým:

instrukčný cyklus sa rozdelí na fázy, ktoré sa postupne vykonajú v na seba nadvazujúcich funkčných blokoch?

Rychlost disku HDD zavisi od 2 parametrov

doba pristupu

rychlost prenosu udajov

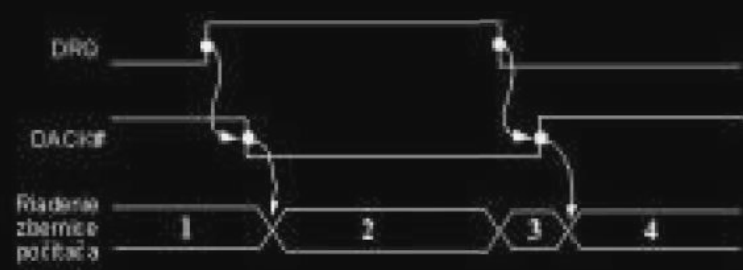

Na obrázku je signálny sled pri prenose DMA. Doplňte riadenie zbernice v jednotlivých úsekoch úsek

zbernica riadi procesor

zbernica riadi riadiaci obvod DMA

zbernica je neriadená

zbernica riadi procesor

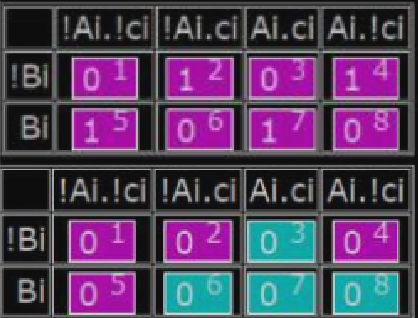

Doplňte hodnoty do Karnaughovej mapy pre i-ty bit binarnej sčitačky.

Si:

Doplňte hodnoty do Karnaughovej mapy pre i-ty bit binárnej sčítačky.

ci+1:

400 300 202 400

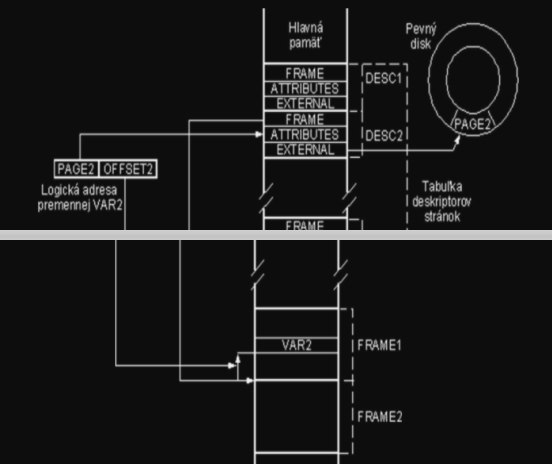

Na realizáciu virtuálnej pamäte sa používajú 2 zákl. techniky. Obrázok reprezentuje techniku s názvom strankovanie pri ktorom je hlavná pamäť rozdelená na strankove ramy

Program a udaje budu rozdelené na bloky …1 dĺžky.

Pri tejto technike vzniká problém … …2 hlavnej pamate.

rovnakej

intergnej fragmentacie

Uvažujte operačnú časť na obrázku. Kolko cyklov zbernice bude potrebné na realizáciu operácie AX := AX + CX za predpokladu, že ALU na obrázku takúto operáciu dokáže realizovať. => …

3

Koľko 3-vstupových logických členov NOR je potrebných na minimálnu realizáciu kombinačného obvodu, zadaného výrazom:

(a+!b+c)(a+b+!c)(!a+!b+c)4

Mikroprogramova riadiaca jednotka

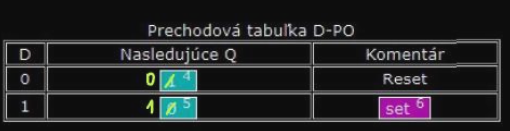

D-PO tabulka

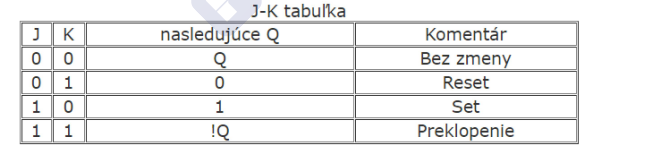

J-K PO tabulka

Uvedie, ktoré z nasledujúcich tvrdení pre automat typu Moore a Mealy sú správne a ktoré nesprávne?

Výstupná funkcia automatu typu Mealy závisí od stavu automatu a od vstupu.

Výstupná funkcia automatu typu Moore závisí od stavu automatu a od vstupu.

Výstupná funkcia automatu typu Moore závisí iba od stavu automatu.

Výstupná funkcia automatu typu Mealy závisí iba od stavu automatu.

true

false

true

false

Rozhranie RS232C ma tieto vlastnosti:

prenos je synchronny

prenos je asynchronny

je paralelne

je seriove

true

true

false

true

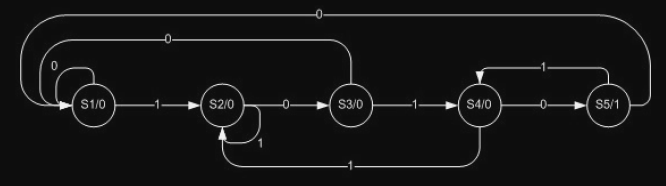

O aký typ automatu sa jedná a v ktorom stave sa bude nachádzať po príchode postupnosti 11001?

V stave S2

Automat typu Moore

Aký počet stavových premenných je nutný na zakódovanie 23 stavov SSO?

menej ako 6

Priamy sposob adresovania operandu znamena, ze:

v adresovej časti inštrukcie je priamo operand

v adresovej časti inštrukcie je určená priamo adresa pamati, na ktorej sa nachadza operand

v adresovej časti inštrukcie je určený priamo register, v ktorom sa nachadza adresa operandu

format inštrukcie bude obsahovat adresovu cas

false

true

false

true

Procesory CISC su charakteristické:

format instrukcie ma spravidla premenlivu dlzku

vyuziva velky pocet adresovacich rezimov operandov

pouziva velky pocet univerzalnych registrov

instrukcny subor je navrhnuty tak, aby podporoval preklad z vyssich jazykov do strojoveho kodu procesora

true

true

false

true

Riadiaca cast procesora s pevnou logikou je charakteristická:

využíva sa naj ma pri procesoroch typu RISC

maximálnou dosiahnutelnostou operačnou rýchlosťou

univerzálnou strukturou riadiacej jednotky

flexibilitou pri modifikácii funkcii riadiacej jednotky

true

true

false

false

Rozhranie CENTRONICS ma tieto vlastnosti:

je spravidla jednosmerne

je asynchronne

je paralelne

je seriove

true

true

true

false

Na realizáciu virtuálnej pamäte sa používajú 2 zákl. techniky. Obrázok reprezentuje techniku s názvom …1 pri ktorom je hlavná pamäť rozdelená na …2

Program a údaje budú rozdelené na bloky …3 dĺžky. Pri tejto technike vzniká problém … 4 … 5 hlavnej pamät

strankovanie

strankove ramy

rovnakej

internej

fragmentacie

Registrovy sposob adresovania operandu znamena, ze:

v adresovej casti instrukcie je zakodovany register, v ktorom sa nachadza operand

v adresovej casti instrukcie je operand

v adresovej casti instrukcie je urceny priamo register, v ktorom sa nachadza adresa pamati operandu

true

false

true

Prúdové spracovanie inštrukcie je charakteristické tym, ze

inštrukcie sa nedelia nafázy ale viacero inštrukcii sa naraz paralelne vykonáva v na seba nedvazujucich funkčných blokoch

naraz sa paralelne vykonávajú viacere inštrukcie, ktoré v danom case su v rôznych fazach vykonávania

inštrukčný cyklus sa rozdelí na fázy, ktoré sa naraz paralelne vykonajú v na seba nadväzujúcich funkčných blokoch

inštrukčný cyklus sa rozdelí na fázy, ktoré sa postupne vykonajú v na seba nadväzujúcich funkčných blokoch

false

true

false

true

Priamy sposob adresovania operandu znamena, ze

format inštrukcie bude obsahovat adresovu cast

Operacna Cast procosotA je tvorená

Aritmeticko logickou jednotkou (ALU), registrami a komunikačnými obvodmi

Koľko D-PO obvodov je potrebných na realizáciu SSO s 12-timi stavmi?

4 D-PO

Mikroprogramova riadiaca jednotka procesora je charakteristicka

flexibilitou pri modifikacii funkcii riadiacej jednotky

univerzalnou strukturou riadiacej jednotky

Procesory CISC su charakteristické

format inštrukcie ma spravidla premenlivú dlzku

využíva velky počet adresovacich režimov operandov

instrukeny subor je navrhnuty tak, aby podporoval preklad z vyssich jazykov do strojoveho kodu procesora

Vystupna funkcia automatu typu Mealy závisi od stavu automatu a od vstupu.

Vystupná funkcia automatu typu Moore závisi iba od stavu automatu

Zapis do registra moze byt riadeny alebo neriadeny, pricom kazdy z nich moze byt synchronizovany alebo nesynchronizovany:

synchronizovany zapis sa moze uskutocnit pri aktivnej hodnote synchronizacnej premennej CLK

neriadeny nesynchronizovany zapis je zapis do registra, ktory sa sklada z asynchronnych preklapacich obvodov

Na akom principe je realizovana pamatova bunka v dynamickej polovodicovej pamati RWM?

udaj sa uchovava vo forme naboja na parazitnej kapacite tranzistora MOS

Preklapaci obvod S# - R# :

sa pri kombinaci hodnot S#=0, R#=1 nastavi na hodnotu 1

ma na vstupe zakazanu kombinaciu hodnot 00

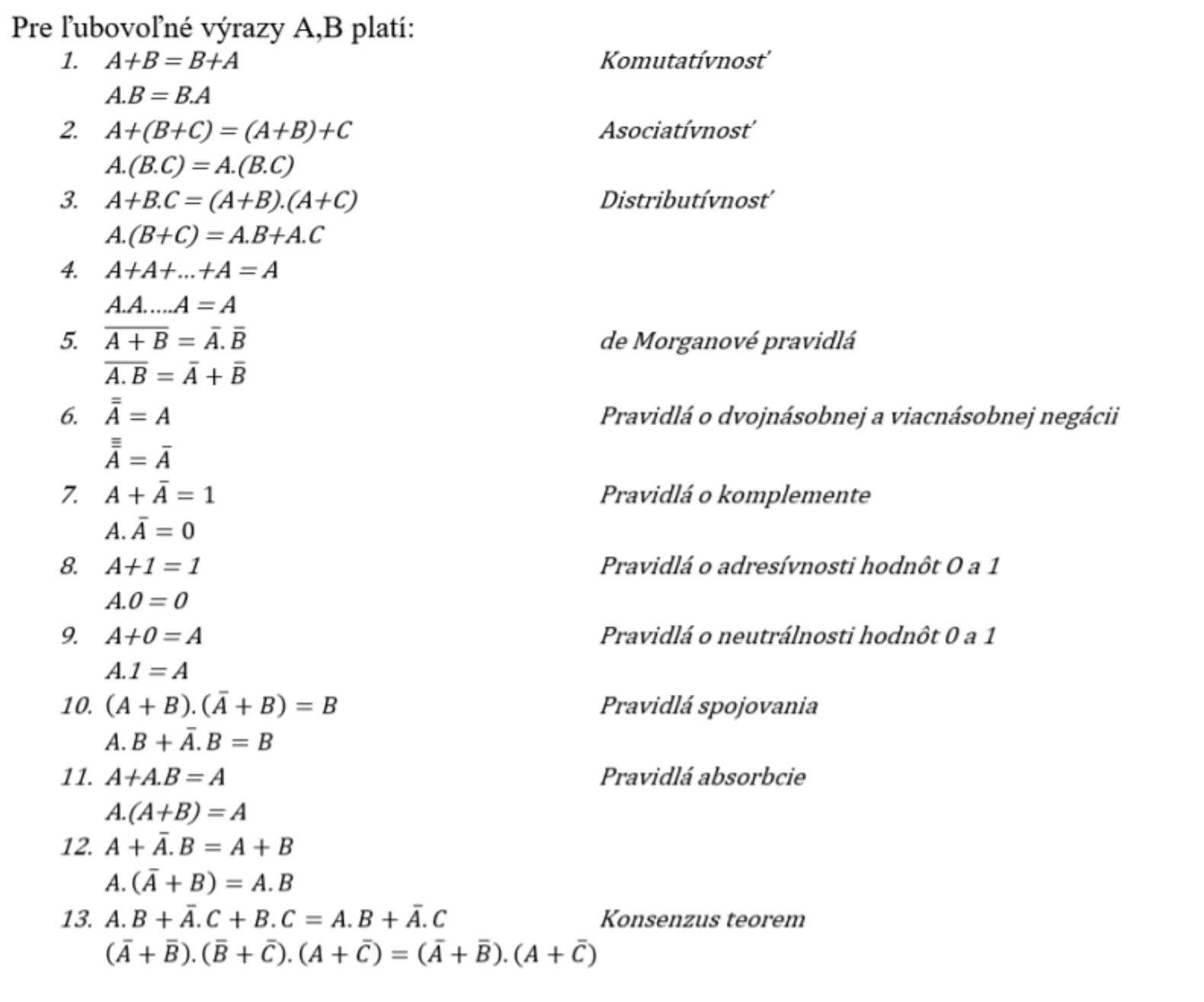

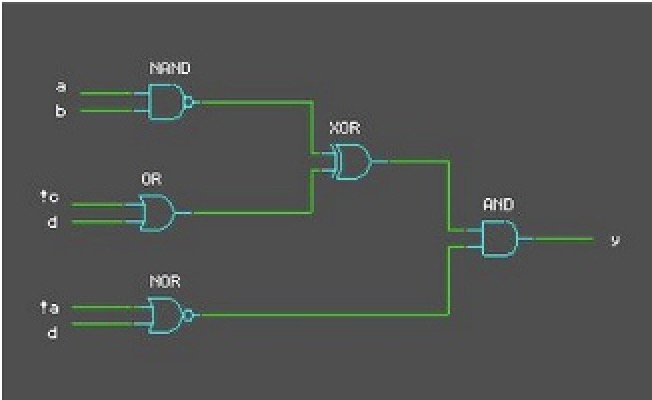

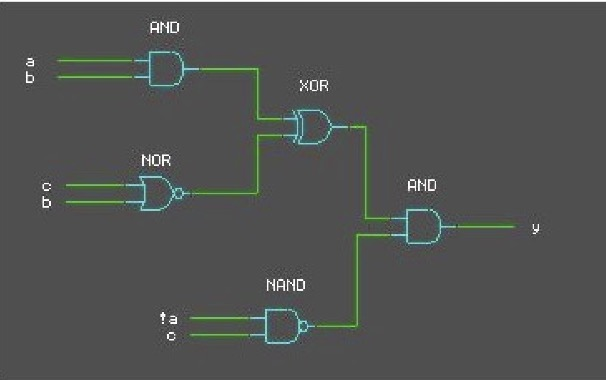

y = a !b c !d + a b !c !d

y = a b + !b !c

Riadiaca cast procesora s pevnou logikou je charakteristická:

využíva sa najma pri procesoroch typu RISC

maximálnou dosiahnutelnostou operačnou rýchlosťou

Register ACC slúzi na ulozenie jedného z operandov, alebo medzivýsledku výpotov

Register IR obsahuje práve vykonávanú instrukciu

Priamy sposob adresovania operandu znamena, ze:

format inštrukcie bude obsahovat adresovu cast

v adresovej časti inštrukcie je určená priamo adresa pamati, na ktorej sa nachadza operand

Majme synchrónny sekvenny obvod s periódou synchronizaných impulzov E a Sirkou synchronizaných impulzov š.

Nech šmin je minimálna sirka synchronizaného impulzu, Kmax a Kmin sú hranicné hodnoty oneskoreni kombinanej casti obvodu realizujúcej budiace funkcie preklápacich obvodov, Pmax a Pmin sú hranicné hodnoty oneskoreni, ktoré vznikajú v preklápacich obvodoch (merané od prednej hrany synchronizacnych impulzov po zmenu vystupu preklápacieho obvodu).

Potom pre správnu cinnost synchrónneho sekvenăného obvodu plati

šmin =< š =< Pmin + Kmin

E >= Pmax + Kmax

Prúdové spracovanie inštrukcie je charakteristické

naraz sa paralelne vykonávajú viacere inštrukcie, ktoré v danom case su v rôznych fazach vykonávania

instrukcny cyklus sa rozdeli na fazy, ktore sa postupne vykonaju v na seba nadvazujucich funkcnych blokoch

Registrovy sposob adresovania operandu znamena, ze:

v adresovej časti inštrukcie je zakodovany register, v ktorom sa nachadza operand