(CIE A2 Compsci) Pipelining + interrupts

1/7

There's no tags or description

Looks like no tags are added yet.

Name | Mastery | Learn | Test | Matching | Spaced |

|---|

No study sessions yet.

8 Terms

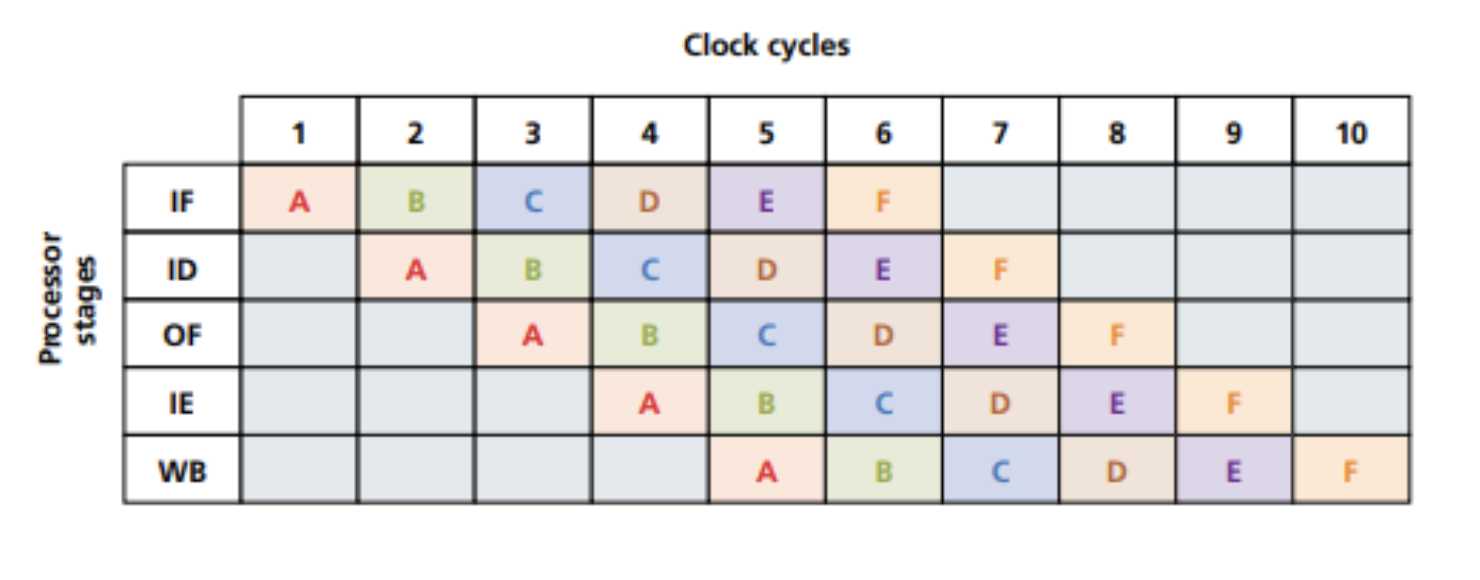

pipelining

a major development related to RISC that improves computer performance in a less complex way by allowing several instructions to be processed in paralllel with zero waiting periods through five single-cycle stages

IF (instruction fetch cycle)

the first single-cycle stage of pipelining

ID (instruction decode cycle)

the second single-cycle stage of pipelining

OF (operand fetch cycle)

the third single-cycle stage of pipelining

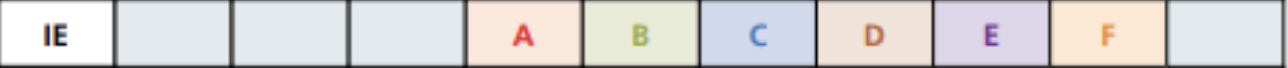

IE (instruction execution cycle)

the fourth single-cycle stage of pipelining

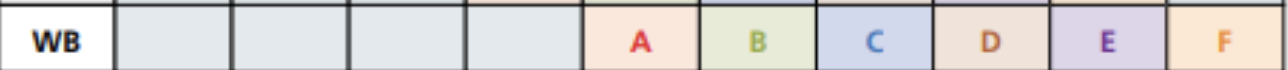

WB (writeback result process)

the fifth single-cycle stage of pipelining

how interrupts are commonly dealt with using pipelining

only the last instruction in the WB stage remains in the pipeline with all the other instructions discarded so an interrupt handling routine can be applied to the remaining instruction and the processor can restart with the next instruction afterwards

a less common way of dealing with interrupts using pipelining

storing the five stages’ current contents in registers so the processor can be restored to its previous status after interrupt servicing