TDT4160 - Datamaskiner

1/80

There's no tags or description

Looks like no tags are added yet.

Name | Mastery | Learn | Test | Matching | Spaced | Call with Kai |

|---|

No analytics yet

Send a link to your students to track their progress

81 Terms

Hurtigbufferbom (direkte tilordnet)

Ved cachemiss må blokken lastes fra hovedminnet og til hurtigbuffer

Hvordan beregne bits rom ved direkte tilordnet hurtigbuffer

Offset = log 2 av størrelse på hver blokk

Indeks = log 2 av antall blokker det er plass til

tag = resterende bits tilgjengelig

Forskjellen på unntak og avbrudd

Et unntak handler om en ikke-forventet endring i kontrollflyten som skyldes f.eks. en ugyldig instruksjon, deling på null eller minnefeil.

Håndtering: Prosessoren stopper utførelsen av den gjeldende instruksjonen

Et avbrudd handler om unntak som skyldes eksterne enheter slik som inn- og utdataoperasjoner som krever oppmerksomhet fra prosessoren. (Tastetrykk og andre I/O enheter)

Håndtering: Prosessoren pauser det gjeldende programmet og lagrer tilstanden, håndterer hendelsen og gjenopptar programmet.

Hvordan regne ut kjøretid?

Tid = antall instruksjoner x CPI x klokkesyklus

Klokkesyklus kan regnes ut fra 1 / klokkefrekvens

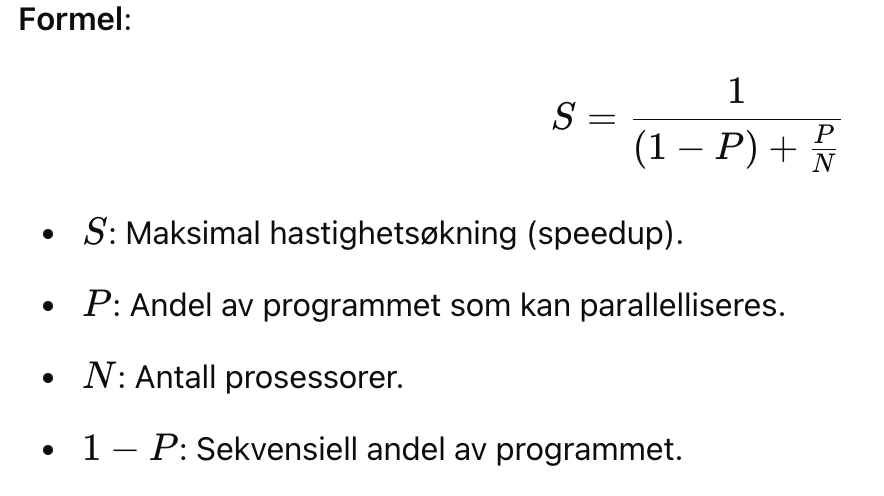

Hva sier Amdahls lov?

Amdahl´s lov sier at den maksimale ytelsesforbedringen av et system er begrenset av den delen av systemet som ikke kan parallelliseres / du kan ikke få en større speed up enn hvor stor del av programmet som er paralelliserbar.

Hva skjer når klokkefrekvensen økes?

Fordel: Hver klokkesyklus blir kortere og tiden det tar å utføre en instruksjon reduserers -> lavere kjøretid

Ulempe: Kritisk sti. For at prosessoren skal fungere korrekt, må lengste signalvei vei være ferdig før neste klokkesykel. Når klokkefrekvens økes, blir det mindre tid tilgjengelig per sykel. Dette kan føre til at noen operasjoner (f.eks. Instruksjonshenting, dekoding eller utføring) ikke rekker å bli ferdig innenfor én sykel. CPI må økes.

Instruksjoner og parallellitet

Refererer til hvordan programmer kan deles opp i flere deler som kan kjøres samtidig, noe som forbedrer ytelsen.

Utregning:

Hva gjør jal? F.eks. jal x1, 128

Jal (Jump and Link) lagrer adressen til neste instruksjon i registeret og hopper til en spesifisert adresse, noe som muliggjør funksjonskall og kontrollflyt.

Her: hopper til adressen PC + 128 og lagrer returadressen i x1.

Funksjonskall

For å kjøre en funksjon, må vi gjennom følgende oppgaver:

Legg parameterne et sted funksjonen kan få tak i dem

Overfør kontroll til funksjonen

Allokere nødvendige ressurser (Registre, minne)

Utfør oppgaven

Legg returverdien til et sted der den som kalte funksjonen kan få tak i dem

Overfør kontroll til kallstedet

Statiske og dynamiske data

Refererer til data som enten er fast i størrelse og plassering (statiske) eller kan endres og tilpasses under programkjøring (dynamiske).

Enkelthet favoriserer regelmessighet

Ved å holde instruksjonsformater få og lengden kort f.eks. gjør dette designet enklere for maskinvare og programvare

“Mindre er raskere”

Ved å minimere antall instruksjoner og registre blir instruksjoner kortere og raskere å dekode og utføre

Prinsippet om lagrede program

sier at både instruksjoner og data lagres i minnet og kan behandles på samme måte. Dette prinsippet muliggjør fleksibel programutførelse.

Båndbredde

Mengden data som kan overføres eller behandles per tidsenhet. Ofte målt i GB/s eller lignende.

Hvordan tekst representeres

Som sekvenser av binære verdier som mappes til en tallverdi i en verditabell

Adresssemodi

Umiddelbar (addi) , bare- eller forskyvning (lw/sw), register (add) og PC-relativ (jal)

Datasti og kontrollenhet

Datsti: utfører de aritmetiske og logiske operasjonene, flytter data mellom minne og registre.

Kontrollenheten: dekoder instruksjonene og styrer datastien

Enkelsykelprosessor

Utfører og gjennomfører én instruksjon per klokkesykel.

Inneholder programteller, instruksjonsminne, registerfil, ALU, dataminne

Utfordringer med enkeltsykelprosessor

Siden den utfører én instruksjon per klokkesyklus må klokkesyklusen være lang nok til å utføre den tregeste instruksjonen

Buss

En buss brukes til overføring av data, adresser og kontrollsignaler mellom komponenter. Det gjør det mulig for CPU og minne f.eks. å kommunisere

ALU-kontrollsignaler

Brukes til å styre operasjonene utført av ALU i en prosessor

00: AND

01: ORD

10: addisjon

11: subtraksjon

Overflyt

Overflyt oppstår når vi ikke kan representere resultatet med det antallet bit vi har tilgjengelig

Oppstår når vi:

legger sammen to positive tall og får et negativt tall

legger sammen to negative tall og får et positivt tall

Heltall: når summen/subtraksjonen går utenfor grensen for signed eller unsigned representasjon

Flyttall: når eksponenten blir for stor

Man kan bruke CarryOut for å oppdage overflyt

Kontroll som tilstandsmaskin

Handler om hvordan en prosessor styrer utførelsen av instruksjoner ved å bruke en sekvens av tilstander som bestemmer hva som skal gjøres i hver syklus.

Flersykelprosessoren deler instruksjonen inn i flere sykluser (henting, dekoding, utførelse, minneoperasjoner, osv.).

Hver syklus representerer en tilstand. Overgangen mellom dem styres av instruksjonen og kontrollsignaler fra datastien.

Flersykel vs. enkeltsykel

Fordeler:

- Effektivitet: Ulike instruksjoner tar ulik tid og flersyklusen tilpasser klokksyklusen

Ulempe:

- Krever større kompleksitet

- Lengre utførelsetid: flere klokkesykluser per instruksjon

Hva er en tilstandsmaskin?

En tilstandsmaskin er en modell som består av:

Tilstander: en tilstand representerer et spesifikt steg i en prosess, f.eks. er IF en tilstand

Overganger: regler som bestemmer når prosessoren beveger seg fra en tilstand til en annen, basert på input

Tilstandsmaskinen sikerer at riktig sekvens følges for hver instruksjonstype. Dette bidrar til å gjøre prosessoren både effektiv og fleksibel for ulike instruksjoner.

SR-lås

Har to innganger, S (set) og R (reset)

Brukes til å lagre én bit med informasjon

S = 1 setter utgangen Q til 1; R = 1 nullstiller Q til 0.

SR-låsen består av to krysskoblete NAND-porter, der utgangen av én port mates som inngang til den andre.

D-vippe

Har én data inngang (D) og en klokkeinngang (CLK)

Data på D overføres til utgangen Q ved en klokke-flanke.

Lagrer data ved hver klokkeovergang.

Låser vs. vipper

Begge lagrer én bit med informasjon.

Forskjellen ligger i hvordan de reagerer på klokkesignaler.

Lås: Reagerer når et signal er høyt.

Vippe: Kantfølsom, dvs. den reagerer kun på stigende eller fallende kant.

Kritisk sti

Den lengste tidsforsinkelsen fra inngang til utgang i en krets. Lengden må være lang nok til å sikre at signaler rekker å bevege seg gjennom hele den “kritiske stien” før neste klokkesignal ellers kan det oppstå feil.

Maksimal klokkehastighet = 1/kritisk sti.

Fordeler og ulemper samlebåndsprosessor

Fordeler:

Flere instruksjoner kan gjennomføres samtidig = høyere gjennomstrømning

Effektiv ressursbruk: alle komponenter er aktive i nesten alle klokkesykluser

Kan håndtere mer komplekse instruksjonssett

Ulemper:

Oppstartskostand: det tar flere klokkesykluser å fylle opp samlebåndet før det får full ytelse

Datafarer siden instruksjoner utføres ut-av-rekkefølge

Kompleksitet

Ulike typer farer

Datafarer: En instruksjon er avhengig av en annen

Strukturfarer: 2 instruksjoner er avhengige av samme maskinvare

Kontrollfarer: ved branch/hopp når prosessoren ikke hvilken instruksjon som er neste

Farer vs avhengigheter

Avhengigheter handler om når én instruksjon er avhengig av tidligere instruksjoner

Farer oppstår i samlebåndet på grunn av avhengigheter

Datafarer

Oppstår pga. av avhengigeter mellom instruksjoner.

Løsning: Forwarding eller stalling

Kontrollfarer

Oppstår når prosessoren ikke vet hva som er neste instruksjon —> branch/hopp

Løsninger:

Prediksjon, statisk og dynamisk

Stalling

Håndtering av farer

Unngåelse; Unngå situasjoner/design som fører til farer.

Stalling; pause samlebåndet til faren er løst, nop-operasjoner/bobler

Videresending; send data direkte fra ALU-resultatet (EX-steget) til instruksjonen som trenger dataen i stedet for vente til det blir lagret i registeret

Prediksjon; Gjett utfallet i stedet for å vente, statisk og dynamiske typer gjett.

Kontroll i en samlenbåndsprosessor

Kontrollsignaler genereres i ID.

Pipeline-registers holder kontrollsignalene for hver instruksjon.

Presise unntak

Et unntak er presist dersom:

Alle instruksjoner frem til unntaket har blitt utført

Ingen instruksjoner etter har blitt fullført

Da kan programmet løse unntaket og gjenoppta prosessen fra der unntaket ble utløst.

Presis unntak har noen problemer med samlebåndsprosessoren fordi instruksjonene der kan være i ulike stadier.

-→ løsning: flush, dvs. tøm instruksjoner etter unntaket. Lagre adressen til unntaksinstruksjonen.

Presise unntak og ut-av-rekkefølge

Problemet ligger i at presise unntak handler om at alle instruksjoner før er blitt utført korrekt og ingen etter unntaksinstruksjonen har blitt utført.

Utfordringen handler derfor om at instruksjoner kan være fullført i en annen rekkefølge enn de hentes.

Løsning: ROB (Reorder-buffer) som sørger for at resultatene skrives tilbake til registeret i riktig rekkefølge

Parallellitet i tid og rom

Må ikke forveksles med lokalisjon i tid og rom.

Parallellitet i tid:

Flere instruksjoner utføres samtidig i ulike stadier av et samlebånd. F.eks. en instruksjon hentes, mens en annen dekodes.

Parallellitet i rom:

Flere funksjonelle enheter arbeider samtidig på tvers av uavhenige instruksjoner.

F.eks to ALU-er utfører beregninger på separate data samtidig

Forskjell: Parallellitet i tid er utnyttet i samlebåndet; parallellitet i rom er utnyttet i prosessoren med to ALU-er.

Hva er RAW?

En instruksjon prøver å lese en verdi som før en annen, tidligere instruksjon har fått skrevet ferdig.

Håndtering: stalling, videresending, register renaming

WAW

To instruksjoner skriver til det samme registeret, men i feil rekkefølge.

Oppstår som konsekvens av ut-av-rekkefølge

Løsning: register renaming

WAR

En fare som følge av at en instruksjon skriver til et register før en tidligere instruksjon rekker å lese det.

ppstår i ut-av-rekkefølge-prosessorer

Løsning: register renaming, ut-av-rekkefølge-kontroll

Register renaming

løser WAW og WAR farer ved å tilordne fysiske registre til logiske registre?

Hver instruksjon får sitt eget fysiske register noe som sikrer uavhengighet mellom dem

Static-multi-issu prosessorer, fordeler og ulemper

Kompilatoren planlegger hvilke instruksjoner som skal utføres parallellt. Benytter seg av instruksjonsplanlegging for å unngå farer

Fordeler:

Bidrar til å redusere farer

Effektiv ved optimalisert kode

enklere å implementere enn dynamiic multi-issue prosessor

Ulemper:

Avhengig av kompilatorens effektivitet

Mindre fleksibilitet for dynamiske avhengigheter

Forskjell fra dynamic: avhengig av kompilatoren vs dynamic som er avhengig av maskinvarelogikk

Hva er en dynamic-multi-issue-prosessor og fordelene

En prosessor som kan utføre flere instruksjoner samtidig.

Dynamisk velger hvilke instruksjoner som skal utføres samtidig, basert på:

Avhengigheter mellom instruksjoner

Tilgjengelig maskinvare

Utfører instruksjoner i en optimal rekkefølge: Instruksjoner utføres i en annen rekkefølge enn de er skrevet, så lenge avhengigheter respekteres.

Benytter seg av ROB, som sikrer at resultater skrives tilbake til registere i riktig rekkefølge.

+ Reservation stations

+ Register renaming

Fordeler:

Effektiv utnyttelse av maskinvare

Håndterer avhengigheter bedre enn static-multi-issue-prosessorer

Implementering: Ut-av-rekkefølge

Henter og dekoder instruksjonen (i rekkefølge), men utfører dem så snart alle nødvendige operander er tilgjenglige, uavhengig av rekkefølgen de ble hentet i.

Bruker reservation stations for å holde instruksjoner som venter på data, og register renaming for å elimenere WAR og WAW.

Lagrer resultatater midlertidig i en ROB for å sikre at instruksjoner “commites” i riktig rekkefølge og sikrer med dette presise unntak.

Med en slik implementering sikres det at uavhenige instruksjoner utføres parallellt og effektivit, selv om andre instruksjoner er blokkert eller forsinket.

Lokalitet i tid og rom

Lokalitet i rom: hvis en minneadresse blir brukt, er det sannsynlig at nærliggende adresser også vil bli brukt. F.eks. elementer i en Array

Lokalitet i tid: Hvis en minneadresse blir brukt, er det sannsynlig at den samme adressen vil bli brukt igjen i nær fremtid.

Lokalitet oppstår som følge av programstruktur (løkker og variabler som brukes flere ganger) og effektiv koding (programmer er ofte skrevet for å utnytte minneadresser sekvensielt og repetivt

Minnehierarki

Dyre og raske minner på toppen, dyrerere og tregere lenger ned i hierarkiet. Gir en illusjon av stort og raskt minne ved at data som aksessres ofte lagres i de raskere nivåene, mens sjeldne i de tregere.

Utnytter lokalitet-prinsippet.

Datamaskiner har minnehierarki for å holde ytelsen høy, men samtidig kostnaden lav.

Direktetilordnet hurtigbuffer

Mapper hver minneadresse til en spesifikk linje i hurtigbufferen.

Tag: Identifiserer hvilken minneblokk som er lagret

Index: Bestemmer hvilen linje i hurtigbufferen dataene lagres i

Offset: brukes til å hente riktig ord fra blokken

Utnytter lokalitet i rom.

Integrasjon av hurtigbuffer i samlebåndsarkitekturen

Integrert mellom IF og MEM.

Instruksjoner hentes fra instruksjonshurtigbufferen, men data hentes fra datahurtigbufferen

Håndtering av skriveoperasjoner

Write-through: Data skrives både til hurtigbuffer og til hovedminnet samtidig.

- Fordel: enkelt å implementere

- Ulempe: krever høy båndbredde

Write-back: Data skrives kun til hurtigbufferen først, og senere til hovedminnet når blokken erstattes.

- Fordel: reduserer antall skriv til hovedminnet

- Ulempe: Krever en dirty bit for å spore endringer. Hvis dirty-bit er satt, må data skrives tilbake til hovedminnet når blokken fjernes.

Skrive-miss:

Write-Allocate: Laster blokken til hovedminnet før den oppdateres

No-write-Allocate; Skriver direkte til hovedminnet uten å laste blokken

Minneakksesstid og ytelse

et nivå:

AMAT (avrage memory access time) = Hit time +(Miss rate x miss penalty)

flere nivåer:

AMAT=Hit Time1+(Miss Rate1×(Hit Time2+(Miss Rate2×Miss Penalty)))

Settassosiative og fullassosiative hurtigbuffere

Handler om hvordan datamaskinen finner og lagrer data i hurtigbufferen.

Settassosiativ:

Hurtig bufferen er delt inni ulike “sett”, der hver minneadresse kan lagres i én bestemt gruppe (sett) av plasser i hurtigbufferen.

Fullassosiativ:

Data kan lagres hvor som helst i hurtigbufferen.

Når prosessoren leter etter data, sjekker den hele hurtigbufferen for å finne det

Krever sammenligning av tag med alle linjer, noe som gir høyere kompleksitet

Når data kan lagres i flere linjer (settassosiativ) eller hvor som helst (fullassosiativ), reduseres sannsynligheter for miss = større treffrate

Volatilt minne

Krever strøm for å beholde data

Brukes til rask tilgang, som i hurtigminne (SRAM) og hovedminne (DRAM).

Ikke volatilt minne

Beholder data selv når strømmen er av

Flash-minne (SSD) og magnetisk disk (harddisk)

Brukes for langtidslagring

SRAM

Data beholdes så lenge strømmen er på. Hver bit lagres i en flip-flop (6 transistorer per bit)

Fordeler:

- Veldig raskt

Ulemper:

- Dyrt (krever flere transistorer per bit)

- Tar mye plass

Brukes nærmest prosessoren som hurtigbuffer for rask tilgang

Grunnleggende prinsipper:

Krever strøm for å beholde data

Lagres ved hjelp av flip-flops, som er bygget på 6 bits transistorer per bit

Data leses og skrives raskt yten behov for refresh (slik som DRAM)

DRAM

Data lagres som elektronisk ladning i en kondensator.

Må oppdateres periodisk for å beholde data.

Fordeler:

- mer kompakt og billigere enn SRAM

Ulemper:

- Tregere enn SRAM

Brukes i hovedminne (RAM). Balanserer kapasitet og hastighet

Grunnleggende prinsipper:

Hver bit lagres som en elektrisk ladning i en kondensator

Krever periodisk oppdatering siden ladningen lekker over tid

Mer kompakt enn SRAM fordi én celle bare krever én transistor og én kondensator

Virtuelle adresser

Adresser som programmer ser og bruker.

Håndteres av operativsystemet for å gi programmet en isolert og fleksibel minnevisning.

Brukes som isolasjon mellom prosesser?

Fleksibilitet for programkjøring (kan bruke samme virituelle adressse i ulike prosesser)

Effektiv minneadministrasjon

Fysiske adresser

Faktiske minneadresser i maskinvaren (RAM)

Oversettelse av virtuelle adresser til fysiske

Utføres som en kombinasjon av programvare og maskinvare

Maskinvare:

Søker i TLB (translation lookaside buffer) for rask oversettelse

Programvare (OS)

Hvis en TLB-miss oppstår, bruker operativsystemet sidemappe-tabeller for å finne oversettelsen

TLB - Translation lookaside buffer

En liten hurtigbuffer som lagrer nylige oversettelser fra virutelle til fysiske adresser

Hjelper med å redusere tiden det tar å oversette adresser ved å unngå å slå opp i sidemappe-tabeller hver gang.

Hvordan TLB fungerer

Når en prosessor aksesserer en virtuell adresse;

Sjekker TLB om oversettelsen allerede finnes

TLB hit:

Fysiske registre returneres raskt

TLB miss:

Operativsystemet bruker sidemappe-tabellen til å finne oversettelsen

Resultatet lagres i TLB for fremtidige forespørsler

Fordeler:

Reduserer behovet for langsomme oppslag i sidemappe-tabellen

Gir raskere adresseoversettelse, spesielt fordelaktiv for programmer med høy lokalitet

Parallellitet innad i et program

Handler om å dele opp arbeidet slik at flere deler av programmet kan kjøres samtidig på forskjellige prossessorkjerner. Man kan:

Dele data: kjøre samme operasjon på ulike deler av data

Dele oppgaver: Kjøre ulike oppgaver samtidig.

Målet er å utnytte flere prosessorkjerner for raskere ytelse, men det krever koordingering for å unngå konfliker når trådene deler ressurser.

Utfordringer: Inne i et program er det ofte dataavhengigheter og sekvensiell logikk. Noen deler av koden kan pga. dette ikke parallelliseres, noe som begrenser ytelsesforbedring (Amdahls lov)

Amdahls lov - formel

Sterk og svak skalering

Sterk: måler ytelsesforbedringen når antall prosessorer økes, men problemstørrelsen er konstant. Eks. Hvis et problem kan løses med 4 prosessorer, er det ikke sikkert at økning til 8 prosessorer vil gi dobbel ytelse

Svak: Måler ytelsesforbedringen når både antall prosessorer og problemstørrelsen økes, slik at arbeidsmengden per prosessor holdes konstant.

Eks; Hvis prosessorer analyserer et større datasett når antall prosessorer øker, vil parallellitet bli bedre utnyttet.

Flynns taksonomi, SISD, SIMD, MIMD

Klassifiserer datamaskiner basert på antall datastrømmer og instruksjonsstrømmer

SISD - single instruction, single data:

Én instruksjonsstrøm som behandler én datastrøm

Eks; CPU

SIMD - single instruction, multiple data:

En instruksjonsstrøm som behandler flere datastrømmer samtidig

Eks: GPU

MISD - multiple instruction, single data:

Flere instruksjonsstrømmer som behandler samme datastrøm

Roofline-modellen og operasjonsintensitet

Roofline-modellen visualiserer ytelsen til en applikasjon i forhold til maskinvarebegrensninger, som minnebåndbredde og begrensningskapasitet.

Operasjonsintensitet: forholdet mellom antall beregninger og mengden dataoverføring

Hvis OI er lav er programmet minnebundet

Hvis OI er høy er programmet beregningensbundet (dvs. begrenset av CPU-ytelse)

Synkronisering i flerkjernprosessorer

Synkronisering er nødvendig:

Når flere kjerner jobber på samme data i delt minne, må tilgangene koordineres for å unngå datakorrupsjon (samtidig lesing og skriving) + sikre at resultatene er konsistente

Delt og distribuert minne

Deler prosessorene det fysiske minnerommet?

Ja: delt minne

Nei: distribuert minne

Hva er minnekonsistensproblemet

Handler om hvordan flere prosessorer/kjerner ser data i delt minne.

Oppstår når flere kjerner leser og skriver til samme minneområde samtidig. Da kan det oppstå situasjoner hvor de ser ullike verdier av samme data.

Årsak til problem: Hver kjerne bruke sin egen hurtigbuffer for å øke ytelsen, men dataene kan være utdatert sammenlignet med hovedminnet.

Heterogen datamaskin

Kombinerer ulike typer prosessorer som CPU, GPU, og akseleratorer for optimal ytelse

Løsninger på minnekonsistensproblemet

Minnekonsistensmodeller:

Definerer regler for når oppdateringer til minnet blir synlige for andre kjerner.

Sterk konsistens: Alle kjerner ser oppdateringen i samme rekkefølge (dyrt og tregt)

Svak konsistens: Kjerner må eksplisitt synkroniseres for å se oppdaterte verdier

Synkronisering:

Bruker mekanismer som låser for å sikre korrekt rekkefølge på minneoperasjoner

Cache-koherensprotokoller

Protokoller som sikrer at alle kjerner ser konsistente verdier i sine hurtigbuffere.

Hvorfor er minnekonsistens viktig?

Uten korrekt håndtering av minnekonsistens kan programmer produsere feil, fordi ulike kjerner opererer på motstridende data.

Hvordan håndterer dynamic-issue prosessorer avhengigheter?

Tilpasser seg avhengigheter i sanntid

Utfører instruksjoner ut av rekkefølge

Benytter seg av register renaming og reservation stations

Hvorfor øker settassositive og fullassositative treffraten?

Fordi i en direkte tilordnet hurtigbuffer kan en bestemt minneadresse bare lagres i én spesifikk linje. Hvis en annen adresse også trenger den samme linjen, må dataen fjernes selv om det er plass andre steder i hurtigbufferen.

I et settassosiativt eller fullassosiativt har data flere muligheter for hvor de kan lagres.

Flere steder å lagre data = redusert risiko for miss aka økt treffrate

Hva er prinsippet om lagrede program?

Programinstruksjoner og data lagres i minnet på samme måte.

Programmet blir hentet og utført sekvensielt av prosessoren

Sett opp et kontrollord for instruksjonen lw

ALUSrc: 1

MemtoReg: 1

RegWrite: 1

MemRead: 1

MemWrite: 0

Branch: 0

ALUOp: 0

ALUOp2: 0

Identifiser instruksjon, gitt dette kontrollordet:

ALUSrc: 1

MemtoReg: X

RegWrite: 0

MemRead: 0

MemWrite: 1

Branch: 0

ALUOp: 0

ALUOp2: 0

Sw

Forklar hvordan en CPU kan bruke MSB og LSB for å dekode adresser.

CPU bruker de mest signifikante bitene (MSB) for å velge hvilken minneenhet som skal aktiveres, fordi MSB bestemmer hvilken del av adresserommet som skal brukes. De minst signifikante bitene (LSB) brukes deretter for å finne den spesfikke celleadressen innenfor den valgte minneenheten. F.eks, i et system med flere minnehenhter, kan MSBene avgjøre hvilken SRAM som skal aktiveres, mens LSBene bestemmer hvilken celle som leses i SRAM-enheten.

Hva må man gjøre i samlebåndsarkitekturen for å garantere at programmet uføres korrekt?

Man må passe på at avhengighetene mellom instruksjonene repsekteres. En måte å gjøre dette på er å holde igjen samlebåndet til resultatet er klart.