CPU structure and Instruction Flashcard

1/3

Earn XP

Name | Mastery | Learn | Test | Matching | Spaced | Call with Kai |

|---|

No study sessions yet.

4 Terms

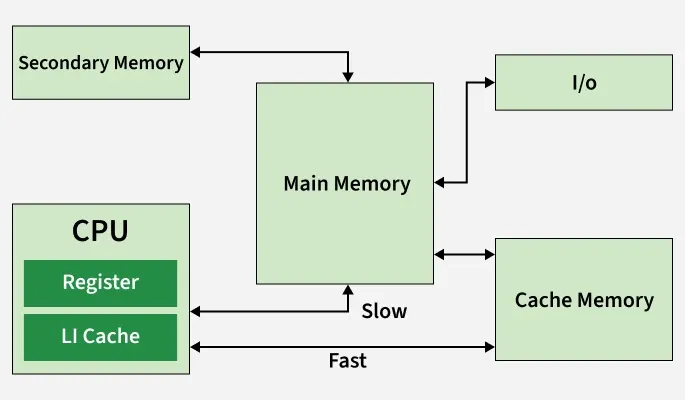

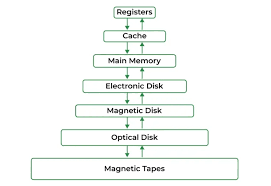

Cache Memory

small, fast memory holding frequently used data to avoid slow trip to RAM

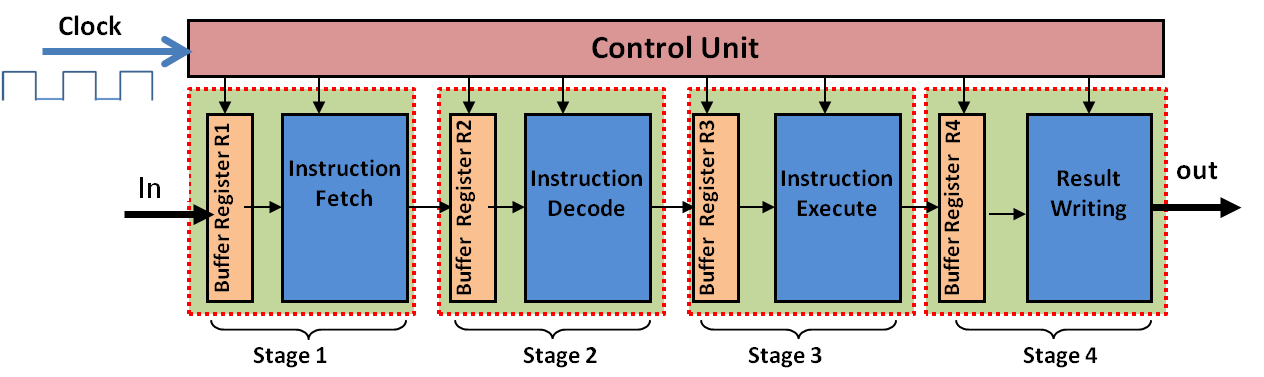

Pipelining

Stages: an instruction moves through dedicated hardware segment for each step

Core function ( Fetch, decode, execute cycle)

fetch: CU gets an instruction from RAM

Decode: CU trasnlate the instruction into micro operation

Execute: ALU perform the operation or data move to memory

Write Back: result is stored in a register or memory

memory management

Allocation: assigning memory block to processes as they start

Tracking: keeping record of which memory parts are used and free

Deallocation: reclaiming memory when processes finish

protection: preventing program from accesssing each other memory

Optimization: Reducing fragmentation and managing virtual memory