Speeding-Up Paging

1/4

Earn XP

Description and Tags

flashcards made from Speeding-Up Paging slides from week 7

Name | Mastery | Learn | Test | Matching | Spaced | Call with Kai |

|---|

No analytics yet

Send a link to your students to track their progress

5 Terms

Speeding-Up Paging

• Major issues faced:

1. The mapping from virtual address to physical address must be fast

2. If the virtual address space is large, the page table will be large

• Observation:

– Most programs tend to make a large number of references to a small number of pages, and not the other way around

– Only a small fraction of the page table entries are heavily read; the rest are barely used at all

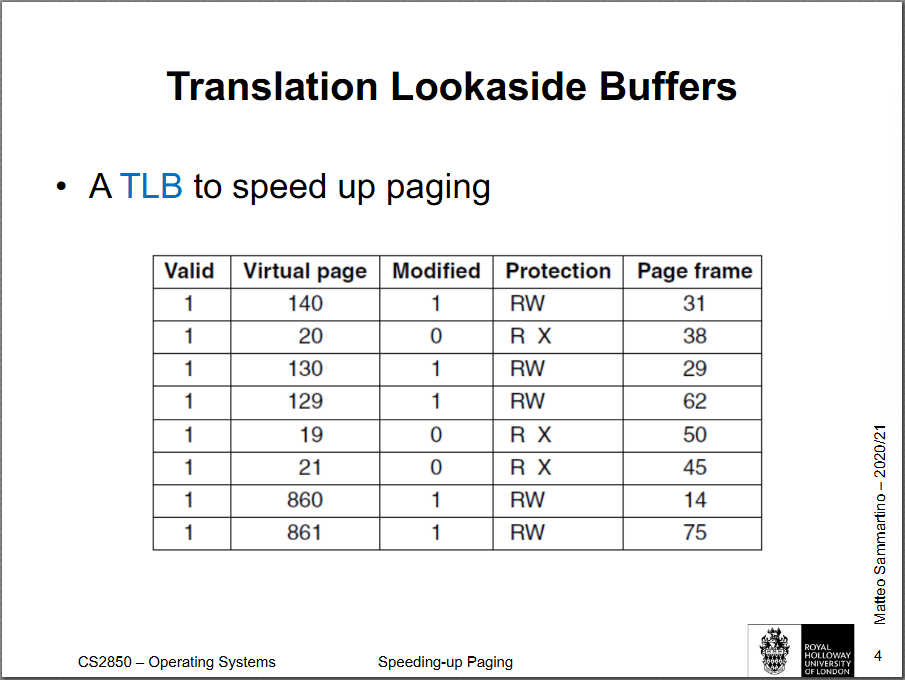

Translation Lookaside Buffers

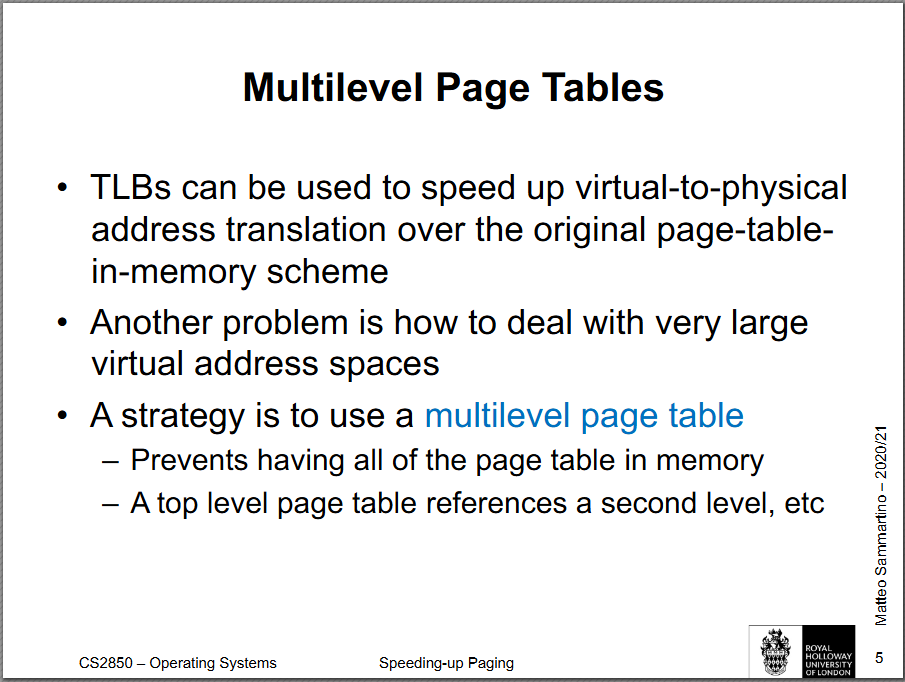

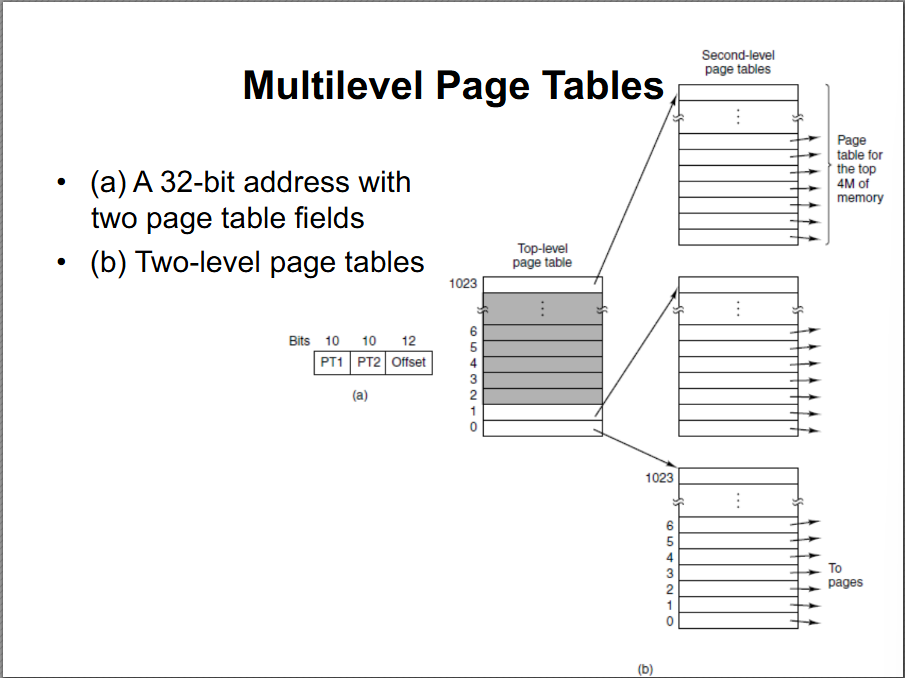

Multilevel Page Tables

Inverted Page Tables

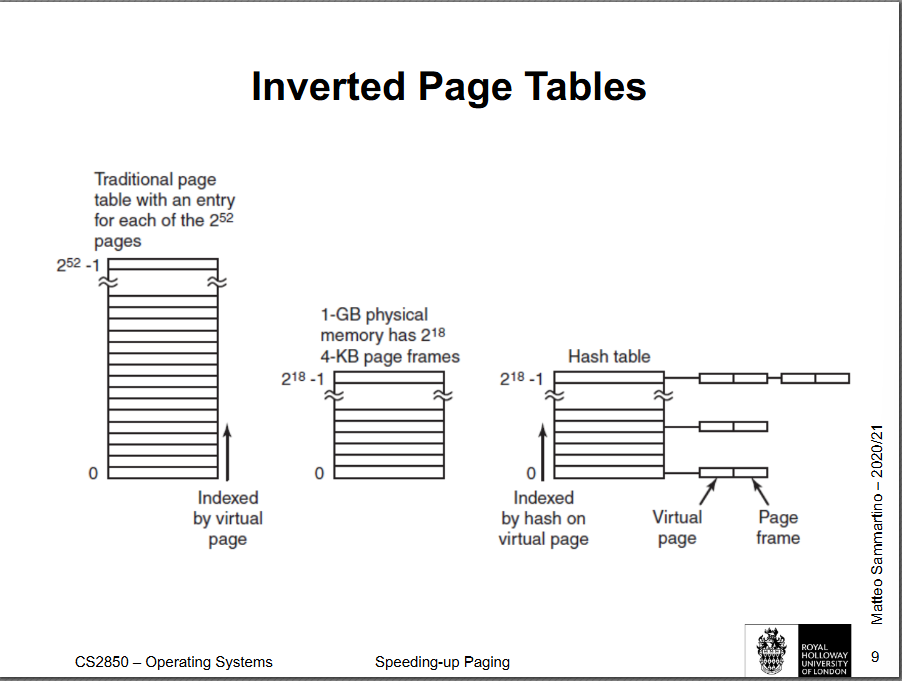

• Goal: Prevent many levels like potentially could occur in the previous approach

• The page table can have one entry per frame in real memory, instead of one per virtual page (inverted page table)

• Saves space

• Virtual-to-physical translation becomes much harder

– A TLB can minimize this

– It is also possible to have a hash table hashed on the virtual address

Inverted Page Tables