Slide 9 - Asynchronous Sequential Circuits

1/19

There's no tags or description

Looks like no tags are added yet.

Name | Mastery | Learn | Test | Matching | Spaced |

|---|

No study sessions yet.

20 Terms

Asynchronous Input

input changes at any time,

eg pushbutton inputs, output driven by a circuit with a different clock

Problems

propagation delay can cause signals to be interpreted as different values in different parts of the circuit

Asynchronous input may violate setup and hold times of flip flop

Synchronized Input

change occur after active clock edge

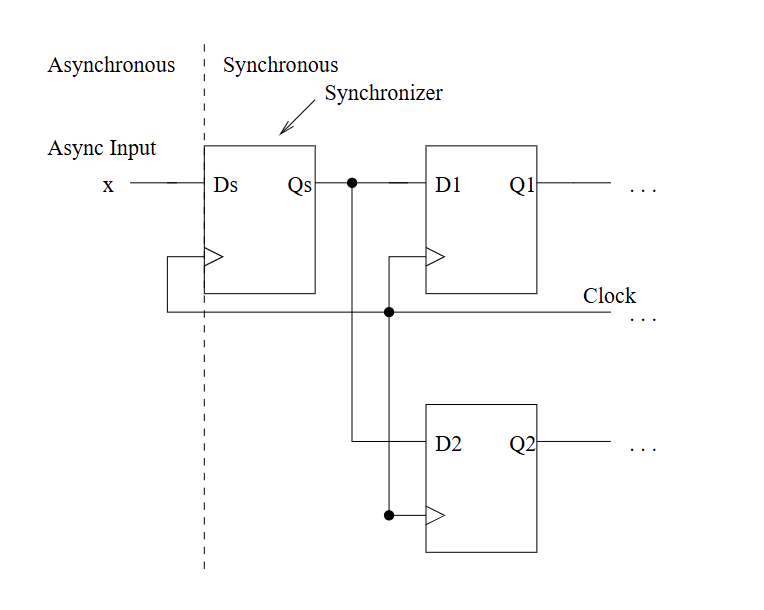

Synchronizing Inputs Idea

put asynchronous input x, through a synchronizer

if they were connected directly, propagation delays could cause Q1 and Q2 to have different latch value

Metastability and Synchronizer

when FF set up times and hold times are violated for synchronizer

Flip flop may enter metastable state, where logic value is neither 1 or 0

will eventually resettle to either 1 or 0 after time

only way to guaranteed way to recover is to reset the entire circuit

Reducing Metastability Problems in Synchronizer

use faster FF with smaller Set up times and hold times

reducing the vulnerable time window

Lengthening the system clock period, or sampling the input at a lower frequency (reduces number of vulnerable time windows)

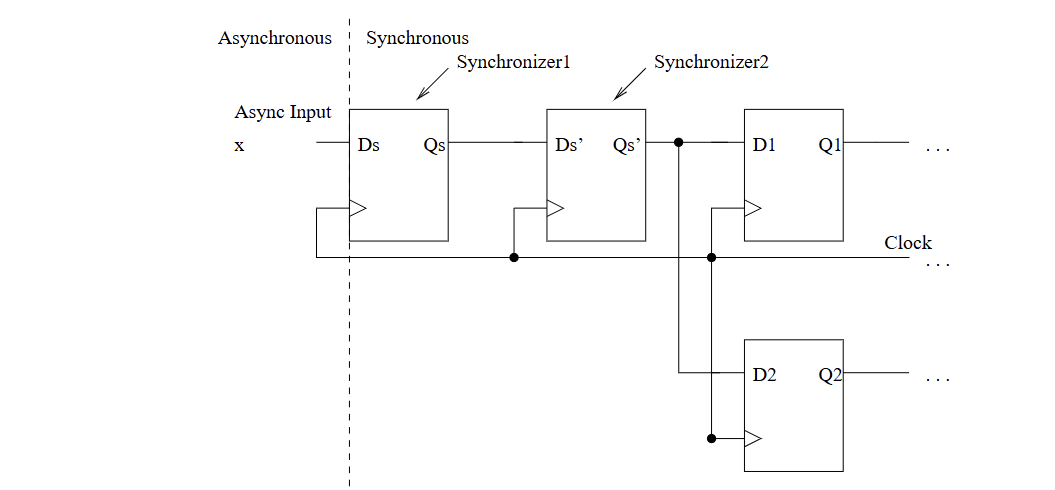

Using a 2 bit shift register as synchronizer, if first FF is metastable state, will usually settle by the time it gets to the next active clock edge

introduced a delay of one clock period on input

A/S sequential Circuits

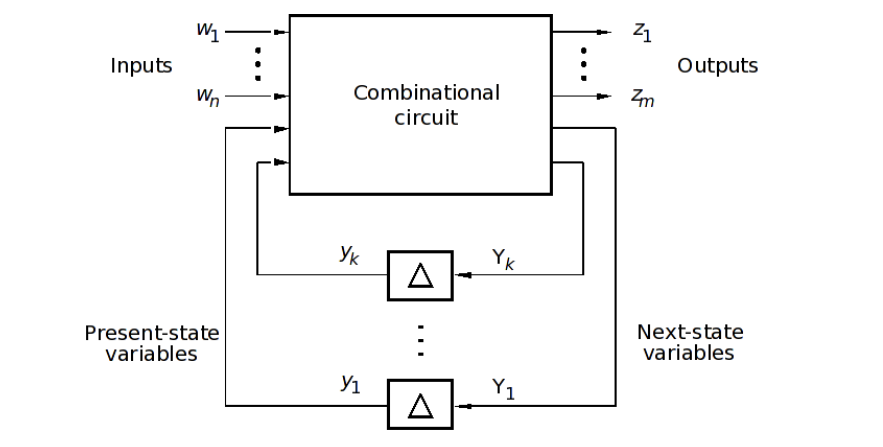

general model; inputs and current state are used by combinational circuits to compute outputs and next state

after time delay, ∆, the next state becomes the current state

for a synchronous circuit, ∆=clck period

Synchronous circuits assume that input do not change to close to active clock edge

for a asynchronous circuit ∆=total propagation delay

Assume;

only 1 input changes at a time

input changes occur sufficiently far apart to allow the circuit to reach a stable state before the next change

Stable state is a state the asynchronous circuit will stay in once reached, until another input changes

Advantages of Asynchronous Sequential Circuits

Speed; no clock involved, speed only depends on propagation delays

Flexibility: different parts of an asynchronous system can operate at different speeds, but in a synchronous system, the clk frequency has to accommodate slowest part

Power Usage; distributing clock signal to all parts adds to power usage up to 30-40%, for a high performance circuit

Disadvantages of Asynchronous Sequential Circuits

Design complexity; difficult to design, and limited tool support

Glitches; race conditions, glitches can cause problems if circuits not carefully design

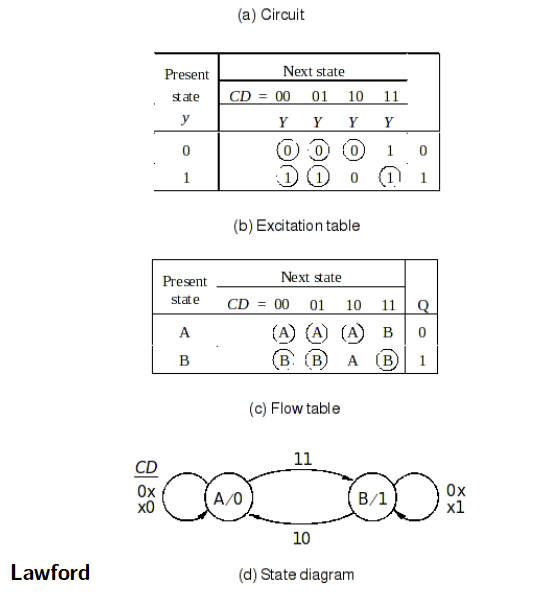

Flow Table

state table of an Asynchronous circuit

a state in a state table is stable for particular set of inputs when the next state = current state

the state is unstable, we circle them in the flow table

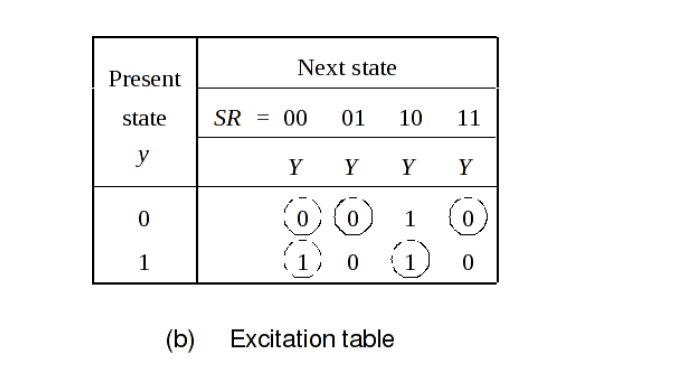

Excitation Table

state assgigned table of a Asynchronous Circuits

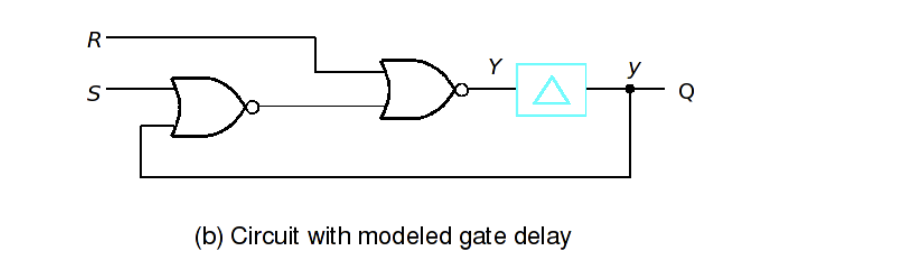

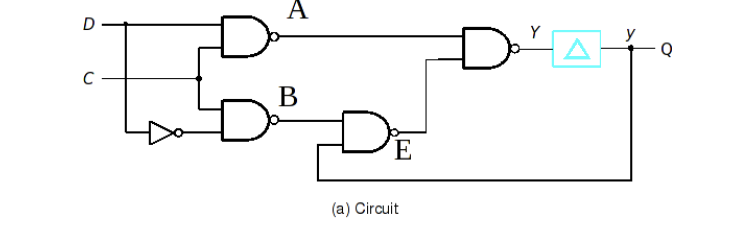

S-R latch as a Asynchronous Circuit

cut the feedback loop and insert a delay elements

creates a time delay of ∆ (equal to the combined propagation delay of the two NOR gates)

treat the NOR gates as ideal, no delay

let y be the input, Y be the next state

after delay of ∆ y is assigned value of Y

Excitation Table for SR latch as an Asynch Sequential

ASYNCHRONOU CIRCUITS HAVE NO RESET

Dp this Example

Race Conditions

when two bits of the presents state change during the next state

requires both buts to change at the same time, but because the circuit is not ideal it won’t

correct outcome depends on which variable changes first

to prevent treat state variable like inputs to circuits, allow only one to change a time )grey code)

Hazards

In a asynchronous sequential circuit, you want to avoid glitches on signals

a glitch is when a signal temporarily takes on the wrong value

Static Hazards

when a signal is NOT supposed to change it’s value, but momentarily does

change to input often has more than one propagation to an output

when one path has a longer prop. delay we may find static hazard

Examine k-maps, when two adjacent 1 (0) are not covered by the same term, there may be hazard

Dynamic Hazard

when a signal is supposed to change value, but there is a small oscillation

you can’t have a dynamic hazard, without static hazard

Prove Static Hazard

Analyze like normal circuit, ignoring the fedback

K-map will show it might have hazard, and where to look for hazard

must draw a timing diagram with delay to show existence

Dynamic Hazards

caused by a circuit with more than two levels, where changes to an input have more than one path to propagate along

to avoid dynamic hazards, design two-level circuit with no static hazards