18: Hardware and Virtual Machines

0.0(0)

Studied by 2 peopleCard Sorting

1/43

Earn XP

Description and Tags

Last updated 8:22 AM on 2/28/23

Name | Mastery | Learn | Test | Matching | Spaced | Call with Kai |

|---|

No analytics yet

Send a link to your students to track their progress

44 Terms

1

New cards

While a program is being executed, the CPU is receiving a sequence of machine-code instructions. What is the responsibility of the control unit in the CPU?

Ensure each machine instruction is handled correctly.

2

New cards

What are the 2 methods a control unit can be designed to allow it to perform its function?

1\. Hardwired solution: Control unit constructed as a logic circuit. Machine code instructions handled directly by hardware 2. Firmware: Control unit to use microprocessing. Control unit contains a ROM component that stores the microinstructions or microcode for mircoprogramming

3

New cards

Complex Instruction Set Computer (CISC)

A single instruction can be more complex and involve more loading of data from memory

4

New cards

Reduced Instruction Set Computer (RISC)

A single instruction is simpler, requiring minimal loading of data from memory

5

New cards

A processor will have an architecture which refers to its physical constructor. A processor will also have a instruction set architecture. What is that concerned with? 4 (choice of instruction set is main factor in distinguishing one instruction set architecture from another)

\-instruction set -instruction format -addressing modes -registers accessible by instructions

6

New cards

What is the main factor for choosing CISC?

Should make writing of a compiler for a high--level language easier

7

New cards

Compare RISC and CISC 10

RISC: Fewer instructions, simpler instructions, small number of instruction formats, single-cycle instructions whenever possible, fixed-length instructions, only load and store instructions to address memory, fewer addressing modes, multiple register sets, hard-wired control unit, pipelining easier vs CISC: more instructions, more complex instructions, many instruction formats, multi-cycle instructions, variable-length instructions, many types of instructions to address memory, more addressing modes, fewer registers, microprogrammed control unit, pipelining more difficult

8

New cards

notes on RISC 5

\-reduced - affects more than just number of instructions -reduction in number of instructions is not major driving force for use -reduction in complexity of instructions is key feature -simplicity of instructions for a RISC processor allows data to be stored in registers and manipulated in them with no resource to memory access other than that necessary for initial loading and possible final storing -simplicity of instruction makes easier to use hard-wiring inside control unit

9

New cards

notes on CISC 4

\-typical CISC architecture contains many specialised instructions -specialised instructions are designed to match requirement of a high-level programming language -specialised instruction require multiple memory accesses which are very slow compared with register accesses -complexity of many CISC instruction makes hard-wiring much more difficult so microprogramming is norm

10

New cards

What is one of the major driving forces for creating RISC processors?

Opportunity they would provide efficient pipelining

11

New cards

Pipelining

Instruction-level parallelism

12

New cards

Pipelining - give more info - give underlying principle

form of parrallelism applied specifically to instruction execution. Underlining principle: fetch-decode-execute cycle can be separated into a number of stages

13

New cards

What is one possibility of a 5-stage model? what are the 5 stages in instruction handling and what else is needed?

processor units: Instruction fetch (IF) Instruction decode (ID) Operand fetch (OF) Instruction execute (IE) Result write back (WB) (Also need clock cycles)

14

New cards

For pipelining to be implemented the construction of the processor must have 5 independent units, each handling of the of the 5 stages identified. This explains?

the need for a RISC processor to have many register sets; each processor unit must have access to its own set of registers.

15

New cards

underway the pipeline is handling 5 stages of five individual instructions. What happens at each clock cycle? Why use pipelining?

the complete processing of one instruction has finished. Without pipeline the processing time would be 5 times longer

16

New cards

What is an issue with pielined processor?

Interrupt handling

17

New cards

The approach where a check for any interrupts is made following the execution of an instruction is applicable to CISC or RISC processor?

CISC processor applicable to RISC processor if no pipelining. However unlikely circumstance.

18

New cards

Using pipelined system described above with 5 processor units. There will be 5 instructions in the pipeline when an interrupt occurs. What are the 2 options for handling the interrupt?

1\. to erase the pipeline contents for the latest 4 instructions to have entered. Then the normal interrupt-handling routine can be applied to remaining instruction. 2. to construct the individual units in the processor with individual program counter registers. Allows current data to be stored for all of the instructions in the pipeline while the interrupt is handled.

19

New cards

You can consider the number of instruction streams and number of data streams to describe different computer architectures. What are the 4 different types?

SISD SIMD MISD MIMD

20

New cards

SISD Def and what does it stand for?

Single Instruction Stream Single Data Stream; a single processor accessing one memory

21

New cards

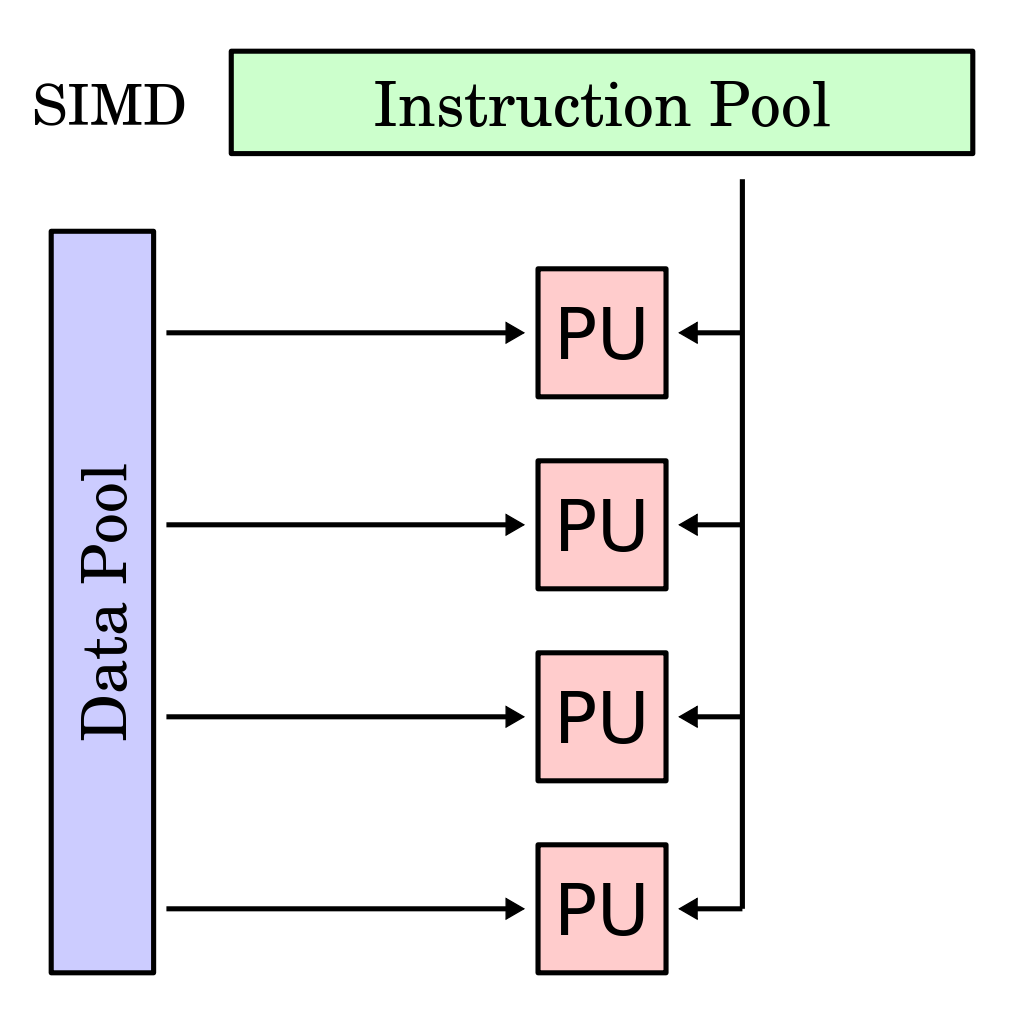

SIMD Def and what does it stand for?

Single Instruction Stream Multiple Data stream; processing of parallel data input requiring one control unit instructing multiple processing units.

22

New cards

MISD Def and what does it stand for?

Multiple Instruction Stream Single Data stream; does not exist in a single architecture.

23

New cards

MIMD Def and what does it stand for?

Multiple Instruction Stream Multiple Data stream; multiple processors asynchronously processing parallel data input.

24

New cards

Describe SISD give ie with \* 2

the typical arrangement in early computers and adapted for earliest microprocessors. Functioning is purely sequential with no parallelism. Ie: 4 3 2 1 \* 2 - 4 3 2 2 - 4342 - 4642 - 8642 instruction used repeatedly instructions sequentially. 1 CPU, 1 ALU

25

New cards

Describe SIMD give ie with \* 2

parallelism applied to the data stream. instruction used once. ie 4 3 2 1 \* 2- 8 6 4 2 1 control unit. Many processing units under supervision of control unit.

26

New cards

give a schematic representation of SIMD architecture

pu (processing unit) sometimes pe ( processing element). arithmetic logic units

27

New cards

There are different options for how the SIMD architecture could be implemented. What are the 2 options?

1\. used in computers called array or vector processors. May have parallel set of registers; one for each data stream. Alternatively, would be a large register perhaps with 64 or 128 bits which could store 4 data values at same time. Parallelism is built into just 1 processor. 2. muti-core processor where 4 individual processors work in parallel. Each processor is likely to have own dedicated cache memory to provide the data stream.

28

New cards

Describe MISD not evidenced in any individual computer architecture design. Give one example.

ie fault-tolerant system. Same data stream could be fed into 2 or more processors. Output would only be accepted if same output was produced by all of the processors

29

New cards

Describe MIMD architecture

Similar to SIMD diagram with more than one processing nit receiving the parallel data streams. Difference is each processing unit doesn't execute the same instruction. Multiple data stream can be provided by a suitably partitioned single memory. Each PU may have a dedicated cache memory

30

New cards

Describe MIMD architecture

Can be implemented in multicomputer systems known as massively parallel computers. These are the systems used by large organisations for computations involving highly complex mathematical processing. They r latest type of 'supercomputer'. Major difference in architecture is instead of having a bus structure to support multiple processors there is a network infrastructure to support multiple computer units. Programs running on the different computers can communicate by passing messages using teh network. An alternative type of multicomputer system is cluster computing using PCS (sometimes referred as 'server farm'.) Have extremely large number of individual processors working in parallel. more than 1 processor unit to execute several program simultaneously

31

New cards

System Virtual Machine (most usual type of virtual machine)

The emulation of computer system hardware (of a real computer) using software.

32

New cards

notes on vm

When a virtual machines is not being used an application program requires support from an OS in order for the program to run on the hardware. Principle of a virtual machine is that a process interacts directly with a software interface provided by an OS.

33

New cards

Give the logical structure for the operation of a system virtual machine

Application programs for virtual machine VM1 - Guest OS for VM1 - Virtual machine VM1 - Virtual-machine implementation software - Host OS - Host hardware Application programs fro virtual machine VM2 - Guest OS for VM2 - Virtual machine VM2 - Virtual-machine implementation software - Host OS - Host hardware

34

New cards

points for diagram 3 application programs implementation software application programs running at same time

1\. application programs are installed with assistance of a guest OS. Guest OS will support the running application by interacting with the vm as though it were the hardware that the guest OS would normally run on. 2. The vm implementation software can be considered to be a utility program which when running is supported by the particular host OS which is specific to the host hardware 3. Can be application programs running at same time directly on host hardware under control of host OS

35

New cards

What is the main advantage of the VM approach?

more than one different OS can be made available on one computer system. Valuable if organisation has legacy systems and wishes to continue to use old software but doesn't wish to keep old hardware. or same OS can be made available many times by companies with large mainframe computers that offer server consolidation facilities. Different companies can be offered their own vm running as a server.

36

New cards

Give a drawback of using a vm? 2

\-time and effort required for implementation -implementation will not offer same level of performance that would be obtained on a normal system

37

New cards

Java virtual machine is an example of a process virtual machine based on a dif underlying concept. Describe

The process virtual machine provides a platform-independent programming environment that allows a program to execute in the same way on any platform. This is specific software that only supports running a java program. A system virtual machine supports any application

38

New cards

What are the differences between a guest operating system and a host operating system? 4

\-Host operating system is providing use of real hardware -a guest os is functioning as though it were providing use of real hardware but in fact is only providing use of a hardware emulation (immitation) -host os is providing support for the running of the vm software -a guest os is ultimately running with support from the host os

39

New cards

Describe 2 tasks that the virtual machine software undertakes

The vm is application osftware, which is running under the control of the host os, which in turn is providing access to the host hardware. There are 2 main functions of the vm: 1. create or detlet an interface that emulates hardware that allows a guest os to be installed. 2. carrying out tasks when an application is running nder the control of a guest os. These include the vm receiving requests fro action from the guest os. These have to be passed through to the host os and subsequently to the hardware. Any result arising from the request has to be received from the host os and passed on the the guest os to pass on to the application

40

New cards

What are 4 different types of parallelism?

Instructions Processors Memory usage Computer Systems

41

New cards

What type of parallelism does pipelining belong to?

Instructions

42

New cards

Explain why interrupt handling is not sstraightforwared in a pipelined system and give a brief account of how problems can be avoided

Interrupts are normally detected an dhandles when an instruction has completed execution. If in a pipelined system one instruction has completed while others have not, interrupt handling routine has to e put into the pipeline. Solutions: erase toher instructions or may have dedicated registers for each strand of the pipeline

43

New cards

RISC processor is likely to be hard-wired. Explain term and which specific part of the processor will be hardwired

Internal workings of the contorl unit logic circuies are used to handle instructions no ROM instide control unit no microprogramming

44

New cards

Give 3 dis of using a VM

\-speed of response needs to be extablisehd but vm will not emulate precisely -when system under pressure from high levels of traffic the perforamnce of hte vm will not accurately predict how hardware would preform -use of a vm invlolves execution of extra code to provide functionality of os so performance degraded