Arithmetic and Logical Operators

1/23

There's no tags or description

Looks like no tags are added yet.

Name | Mastery | Learn | Test | Matching | Spaced | Call with Kai |

|---|

No analytics yet

Send a link to your students to track their progress

24 Terms

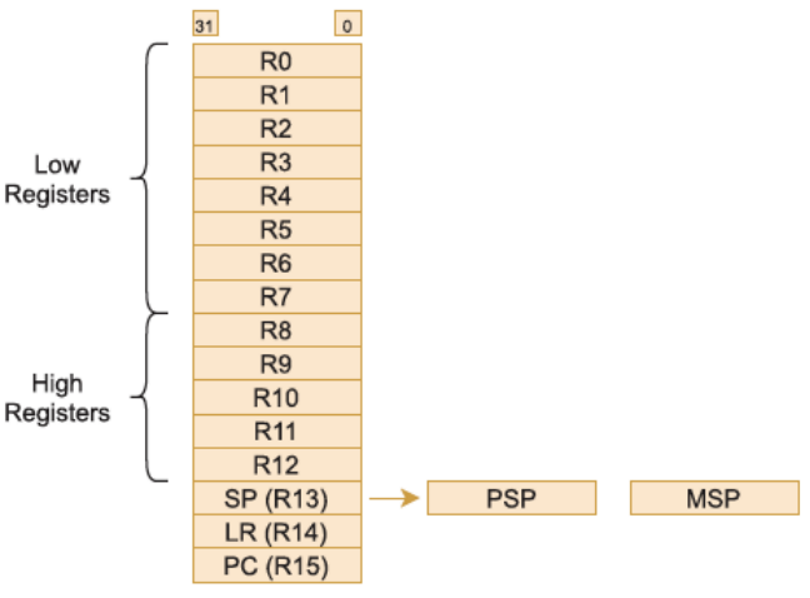

CPU Registers

Registers are represented with a 4-bit number.

R0–R7: lower registers (bit-4 = 0)

R8-R12: higher registers (bit-4=1)

specific instructions store data to them automatically

R13 is the Stack Pointer (SP)

R14 is the Link Register (LR)

R15 is the program counter (PC)

Current Program Status Register (CPSR)

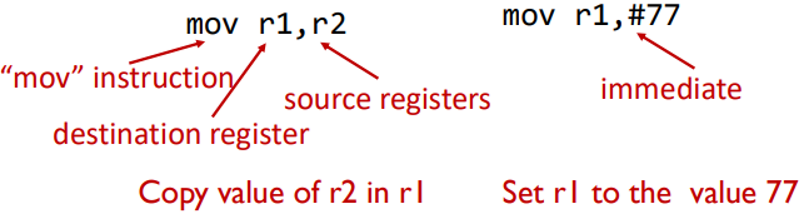

Move

Useful to copy data between registers, or set an immediate to a register

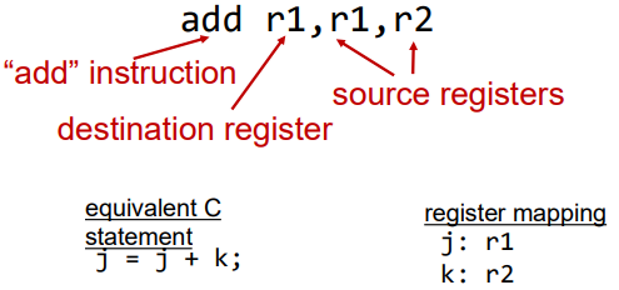

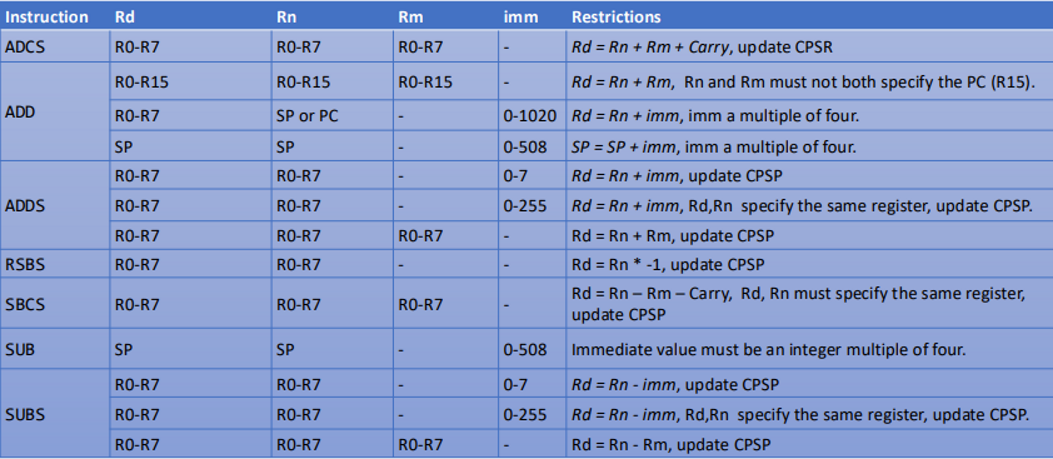

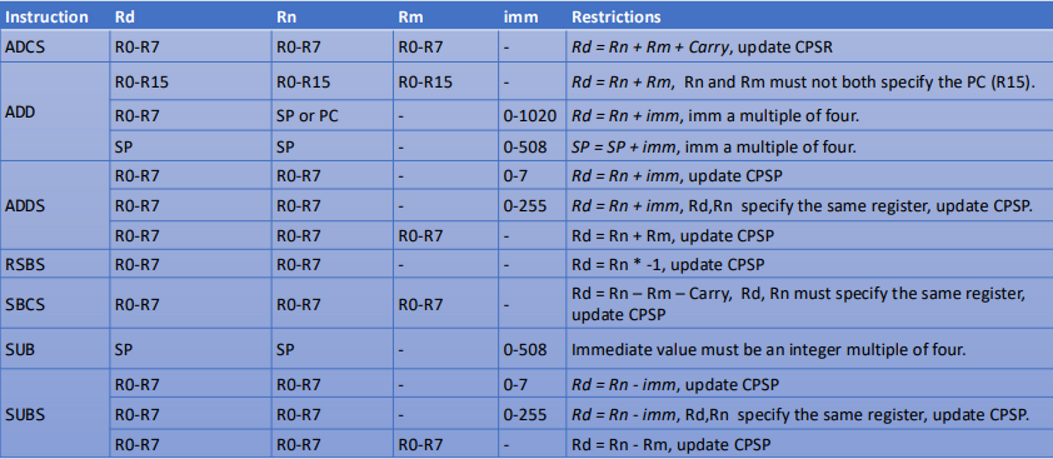

Adding

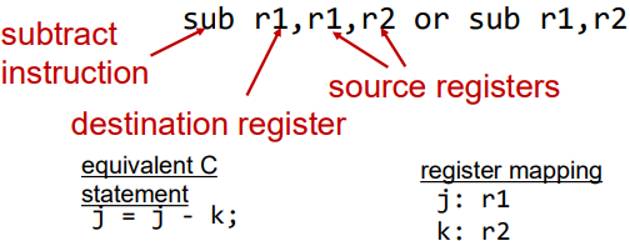

Subtracting

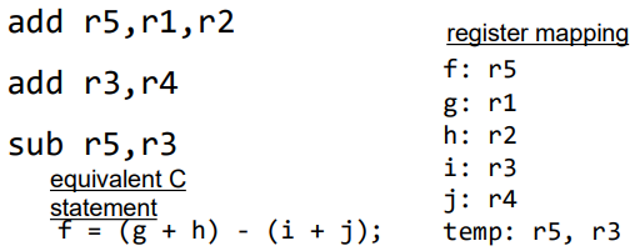

Complex Calculations

must be broken down in smaller steps —> compiler

Number Encoding

The "add" instruction assumes that its operands are encoded using two’s complement

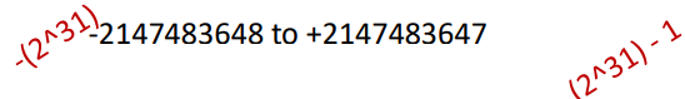

Since each register holds a 32-bit number:

Different instructions can have different expectations for how numbers are mapped or coded in registers

Two’s Compliment

Positive number is directly converted

To obtain negative number flip bits and add 1

To obtain the corresponding positive value flip bits again and add 1

Recording Operation Effects

Sometimes, more than 32-bits is needed for the outcome of an operation

Carry bit

Overflow

Comparison

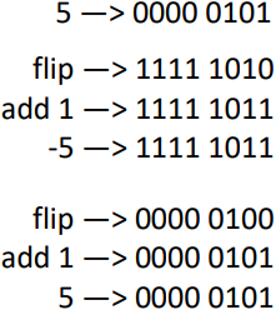

ARM uses a special register (CPSR) to record unusual arithmetic results

We will discuss this a lot when we get to loop and if statements

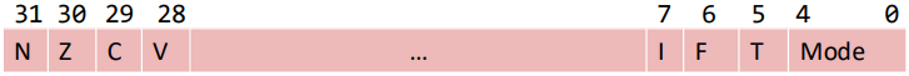

Current Program Status Register (CPSR)

An ARM register that records the state of the program

Arithmetic instructions will affect its value every time

N bit - "negative flag”: instruction result was negative

Z bit -"zero flag”: instruction result was zero

C bit - "carry flag”: Instruction causes a carry-out or borrow

V bit - "overflow flag”: Instruction produces an overflow in 2's complement numbers

Integer Arithmetic Operations in ARM

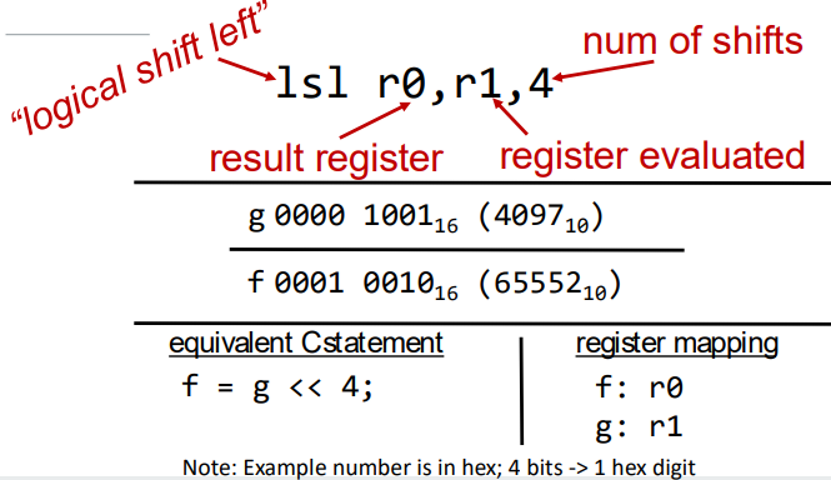

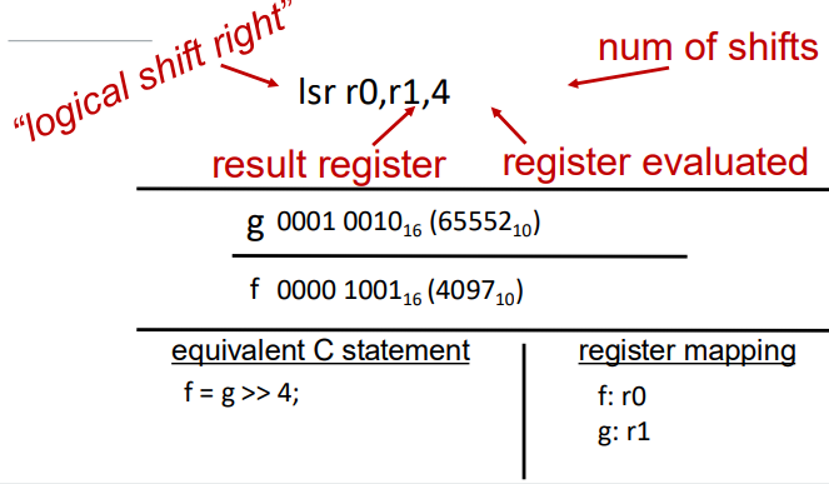

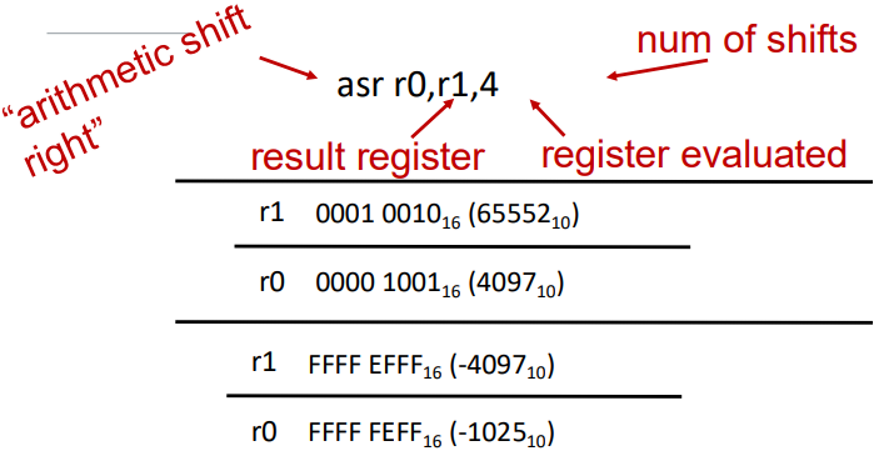

Bit Shifting

Key operation to manage individual bits in a register

Can be used for fast multiplication/division with powers of 2

ASR arithmetic-shift-right

LSL logical-shift-left

LSR logical-shift-right

ROR right-rotation

You can only use R0-R7

Non-immediate operations must use the same source and destination register (i.e, lsl r0, r0, r1)

Logical Left Bit Shifting

Logical Right Bit Shifting

Arithmetic Right Bit Shifting

Bits filled in are the same as the MSB e.g. if MSB is 0 then filled with 0s and if MSB is 1 then filled with 1s

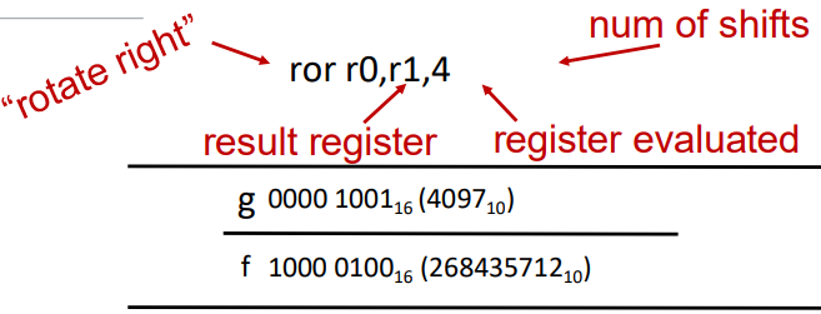

Rotate Right Bit Shifting

Any bit that leaves from the right becomes the MSB

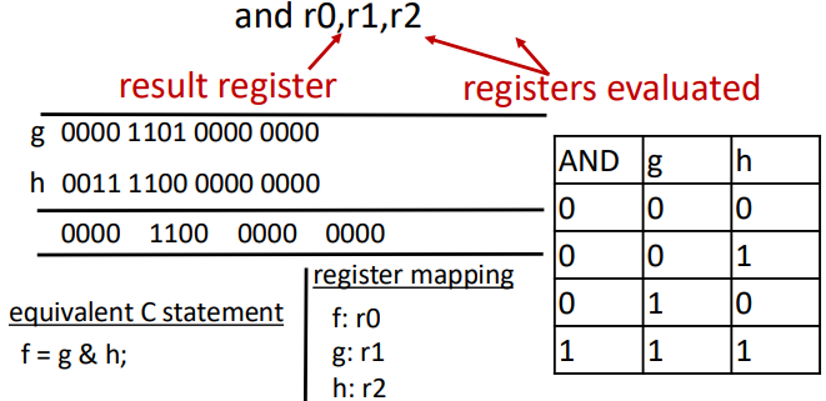

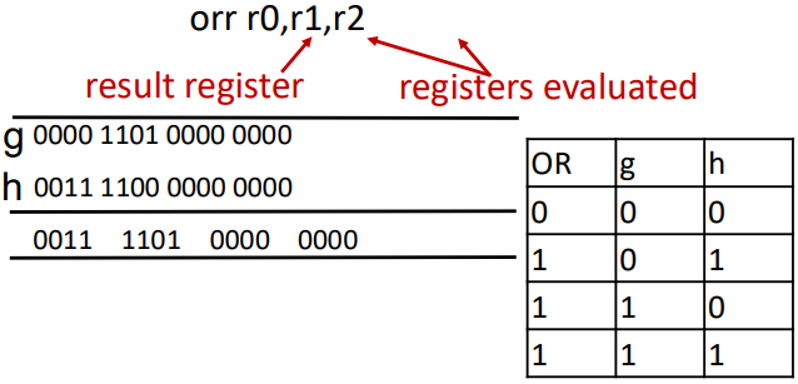

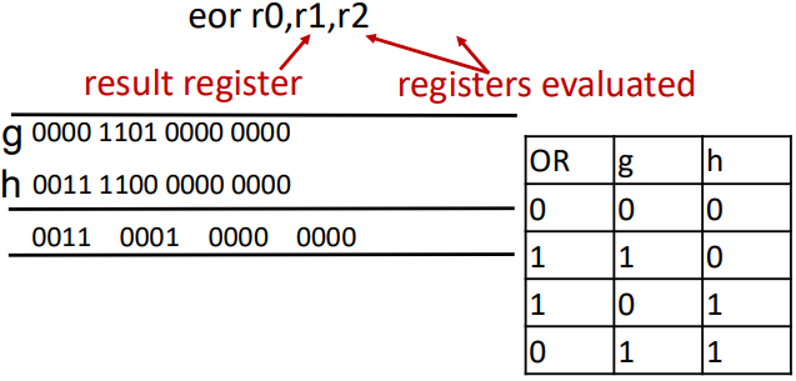

Logical Operators

Using these instructions you can apply all the Boolean operations you learned in the first part of this module

AND: Rn = Rd & Rm

EOR: Rn = Rd ^ Rm (xor)

ORR: Rn = Rd | Rm

BIC: Rn = Rd & ~Rm

update the N and Z flags according to the result for the PCSR

bit-by-bit AND

bit-by-bit ORR

bit-by-bit EOR (Exclusive OR)

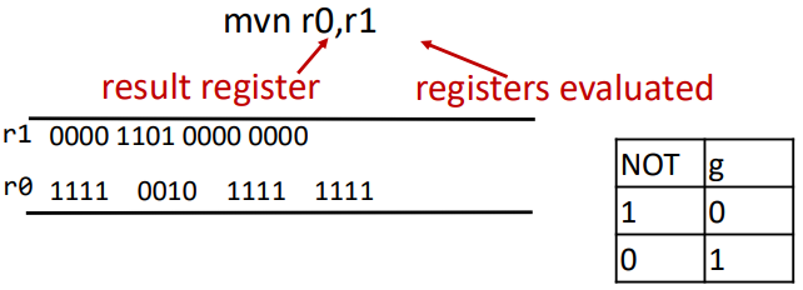

bit-by-bit MVN (Move and Not)

Immediate Operands

Programmers require operations with constants

incrementing a number (e.g. counting, array indexes)

initialising the value held by a program variable

Most instructions can replace one of the input register with an immediate, i.e. an integer value

Because ARM MIPS aims to optimize the space of a program, immediate size varies

You may need to load big values in a register in multiple steps

or use memory to store constants

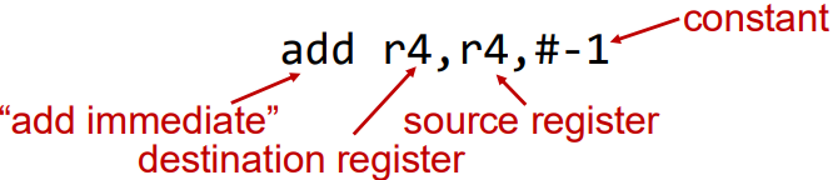

Adding a Constant

Constants are frequently prepended with the symbol #

They are interpreted as a signed integer

Encoded using two’s complement

Integer Arithmetic Operations in ARM

Loading Large Immediates

mov can load values between 0x00000000 to 0x0000FFFF to registers

What about larger integers?

movt can load 16-bit values into the upper 16 bits of a register (lower 16-bits remain the same)

mov r0, 0x1 @ r0 = 0x10000

mov r0, 0xffff @ Loading 0x7fffffff

movt r0, 0x7fff