Sequential circuits

1/13

There's no tags or description

Looks like no tags are added yet.

Name | Mastery | Learn | Test | Matching | Spaced | Call with Kai |

|---|

No analytics yet

Send a link to your students to track their progress

14 Terms

problems with dlatches

level sensitive

synchronization can be difficult

unpredictable: ability to travel thru multiple latches

what are flip-flops

edge triggered

built using latches

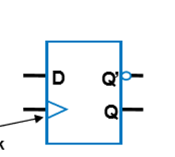

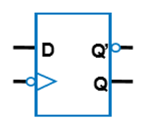

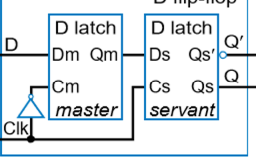

D flip flop

master-slave

rising edge flip flops

falling edge flipflops

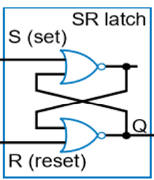

SR Latch

S = 1 sets Q to 1

R = 1 resets Q to 0

problems with SR Latches

SR = 11 makes Q undefined

level sensitive SR latch

S and R have effect when C =1

an external circuit can prevent SR=11 when C =1

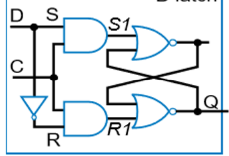

D Latch

SR can’t be 11

Problem with D Latch

C =1 for too long can make new values through too many latches, too short may not result in the bit being stored

D flip flop

only loads D value present at the rising clock edge so values can’t propagate to other flip flops during same clock cycle

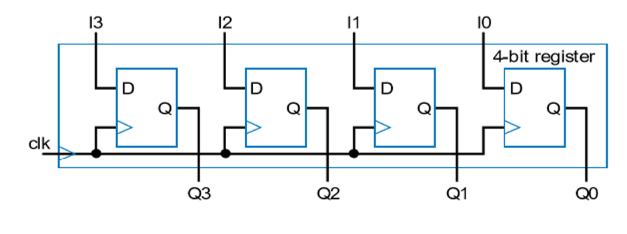

what is is called when multiple flip flops are driven by the same clock cycle

a register

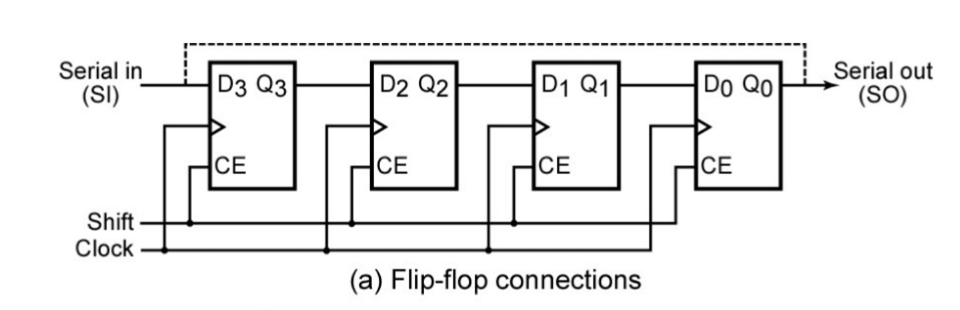

shift register

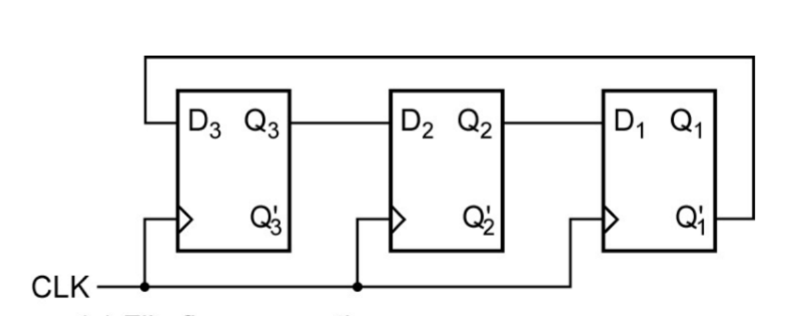

johnson counter