Loops/Flow Control

1/16

There's no tags or description

Looks like no tags are added yet.

Name | Mastery | Learn | Test | Matching | Spaced | Call with Kai |

|---|

No analytics yet

Send a link to your students to track their progress

17 Terms

Pipelining

Widely used way to exploit inherent parallelism inside the CU to speed up the FDE cycle

Program Counter Register

Contains the address of the next instruction to be executed

PC = PC + 4 during fetch to point to next instruction

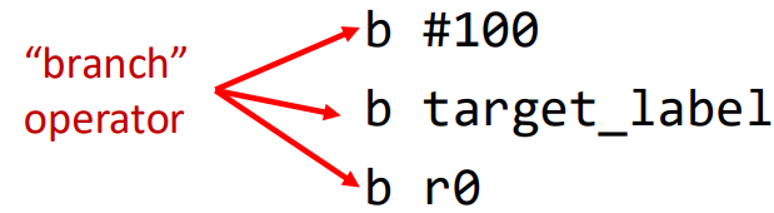

Branching Instruction

Change the PC to point to a different instruction than the next sequential instruction in memory

Updated by a different address in the execute phase

Types of Branches

Unconditional branching: always executes the target instruction

Conditional branch: Perform a jump when a condition is true

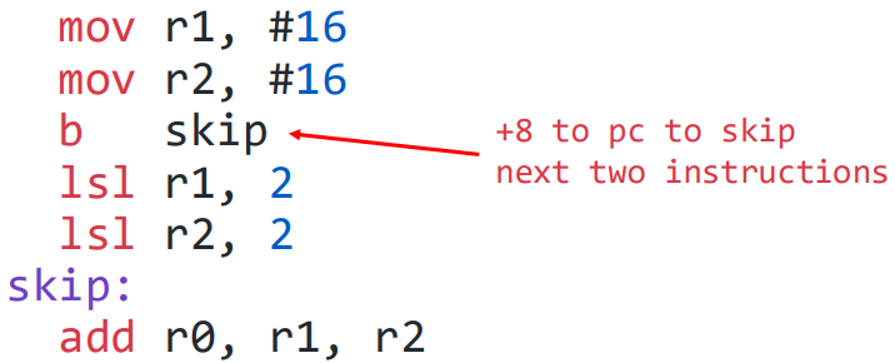

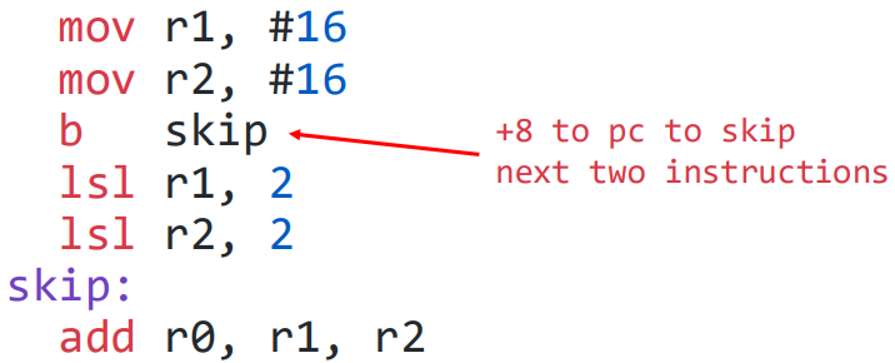

Label

Symbols that represent addresses (like pointers, only with a meaning during assembly phase - if not assembly phase then they are a concept)

The address given is calculated during assembly

Can point both to instructions or data

Developers avoid manually calculating addresses

A reference to one within the same section uses the program counter plus or minus an offset

This is called program-relative addressing

Example - Unconditional Branch

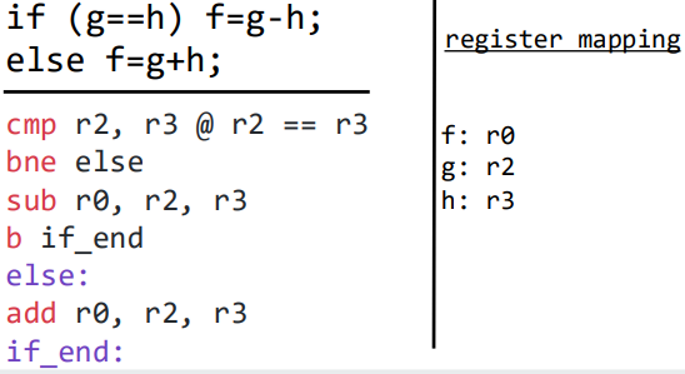

If Statement Code

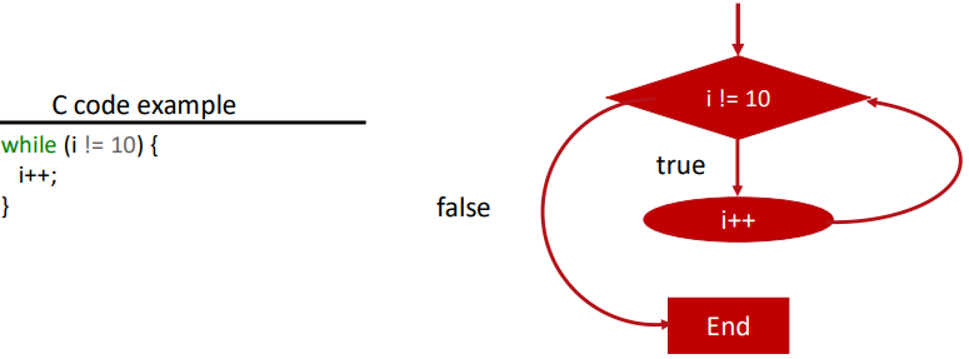

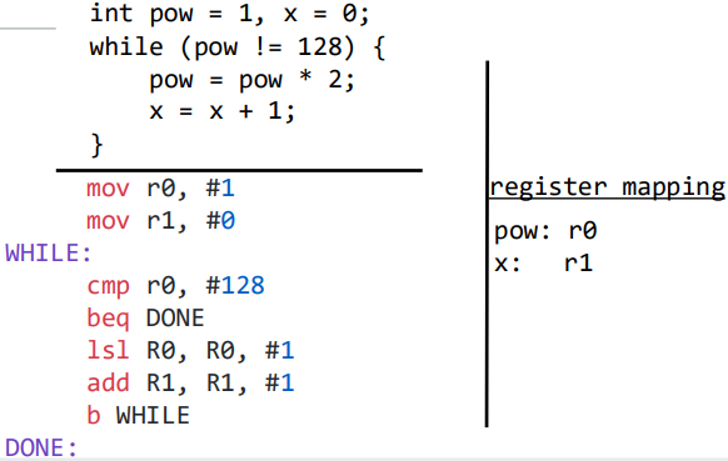

While Loop Code

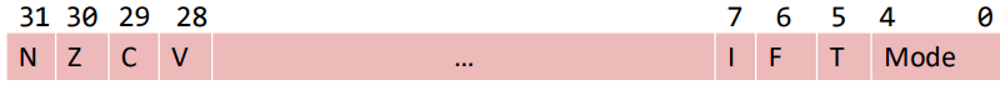

Current Program Status Register (CPSR)

An ARM register that records the state of the program

Arithmetic instructions will affect its value every time

N bit - "negative flag”: instruction result was negative

Z bit -"zero flag”: instruction result was zero

C bit - "carry flag”: Instruction causes a carry-out or borrow

V bit - "overflow flag”: Instruction produces an overflow in 2's complement numbers

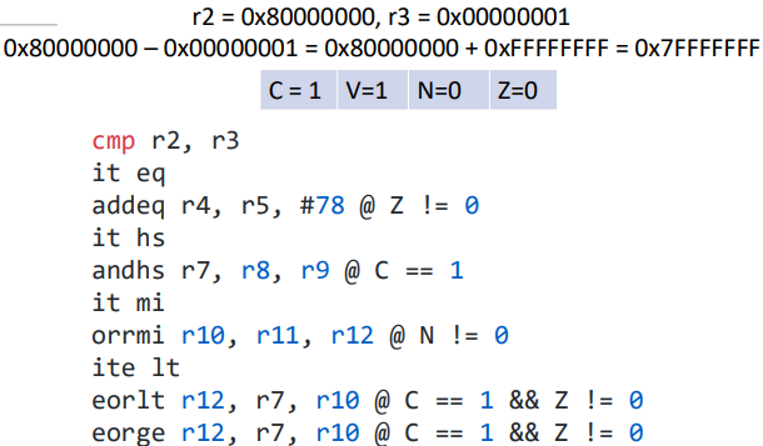

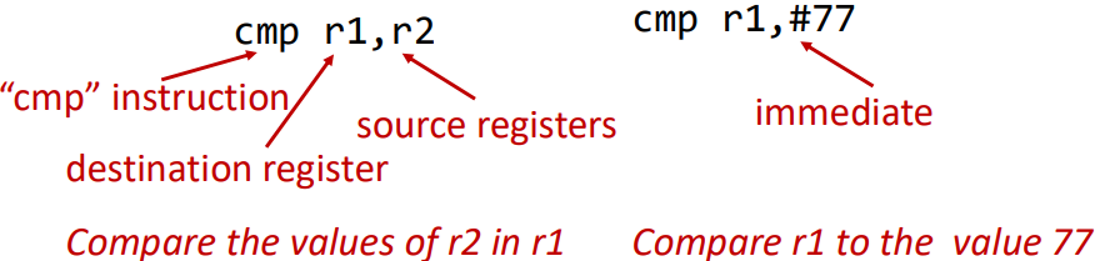

CoMPare

Perform a comparison (substraction), updates the CPSR and discards the result

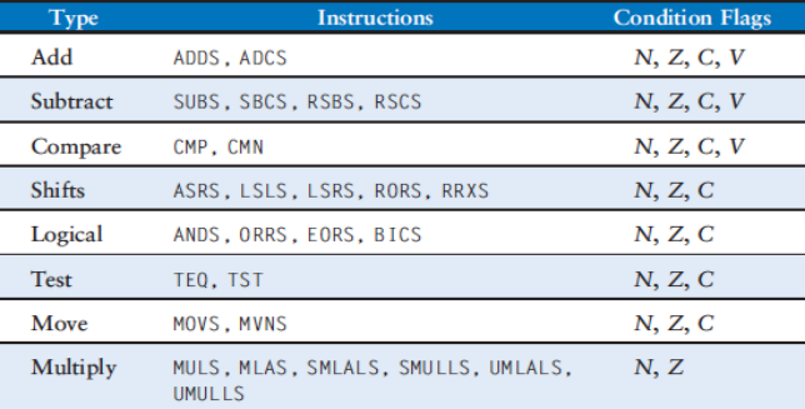

CPSR and Arithmetic Instructions

Conditional Branching

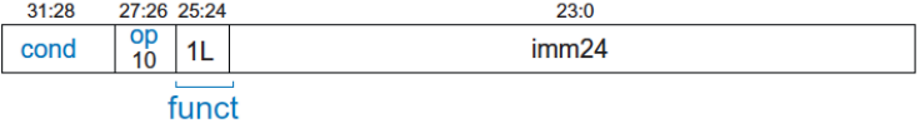

Branch instructions use a single 24-bit signed immediate operand

The remaining 24-bit two’s complement imm24 field is used to specify an instruction address relative to PC + 8

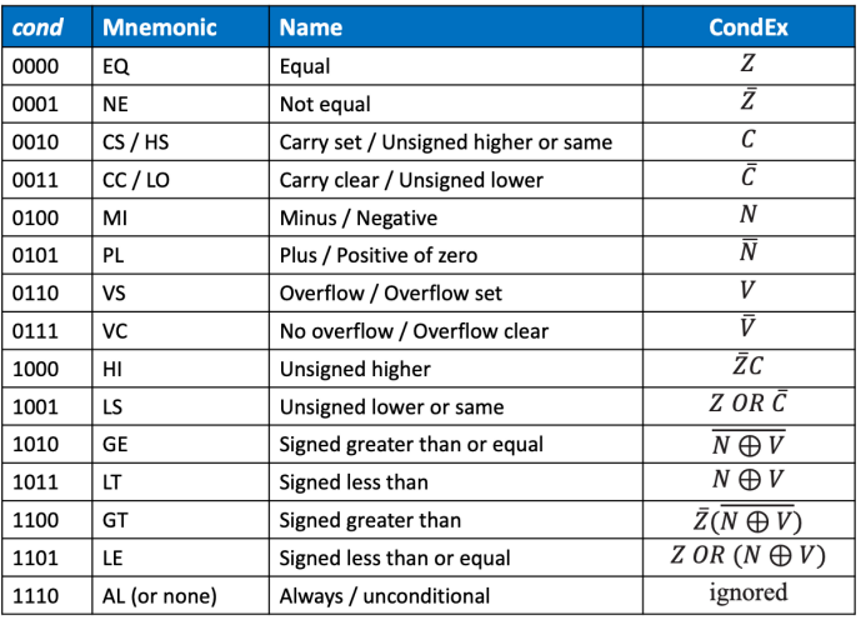

Branching instruction variation: BEQ, BNE,…

Their execution depends on the CPSR condition bits

If condition is false, then branch is skipped

You can construct any branch condition with the mnemonics in the table

Branch Mnemonics

Branch Example - if-then-else

Branch Example - when

Conditional Instruction

ADDEQ, ADDNE

Thumb-2 introduced the If-Then (IT) instruction

providing conditional execution for up to four consecutive instructions. The conditions might all be identical, or some might be the inverse of the others

Instructions within an IT block must also specify the condition code to be applied

Conditional Execution Example