Unidad 2 (copy)

1/35

Earn XP

Description and Tags

Name | Mastery | Learn | Test | Matching | Spaced | Call with Kai |

|---|

No analytics yet

Send a link to your students to track their progress

36 Terms

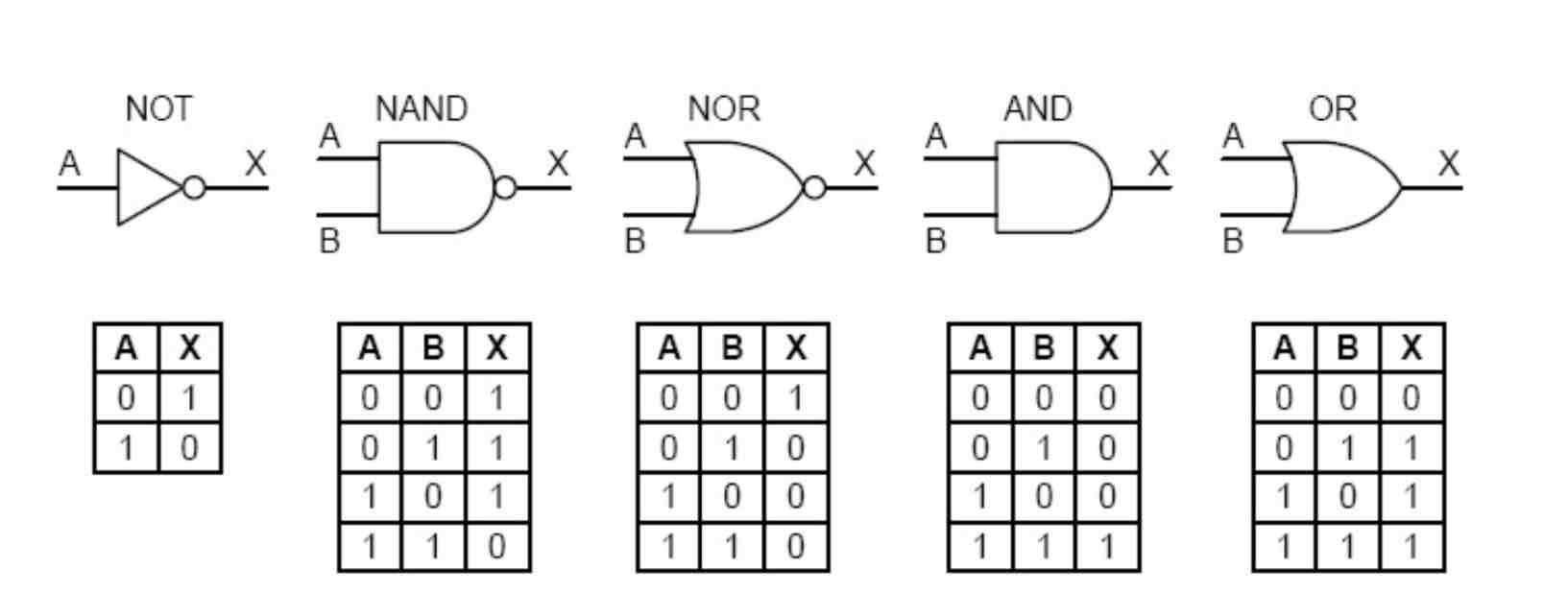

Compuerta Lógica

Circuito eléctrónico que produce como señal de salida una operación booleana sencilla de las señales de entrada.

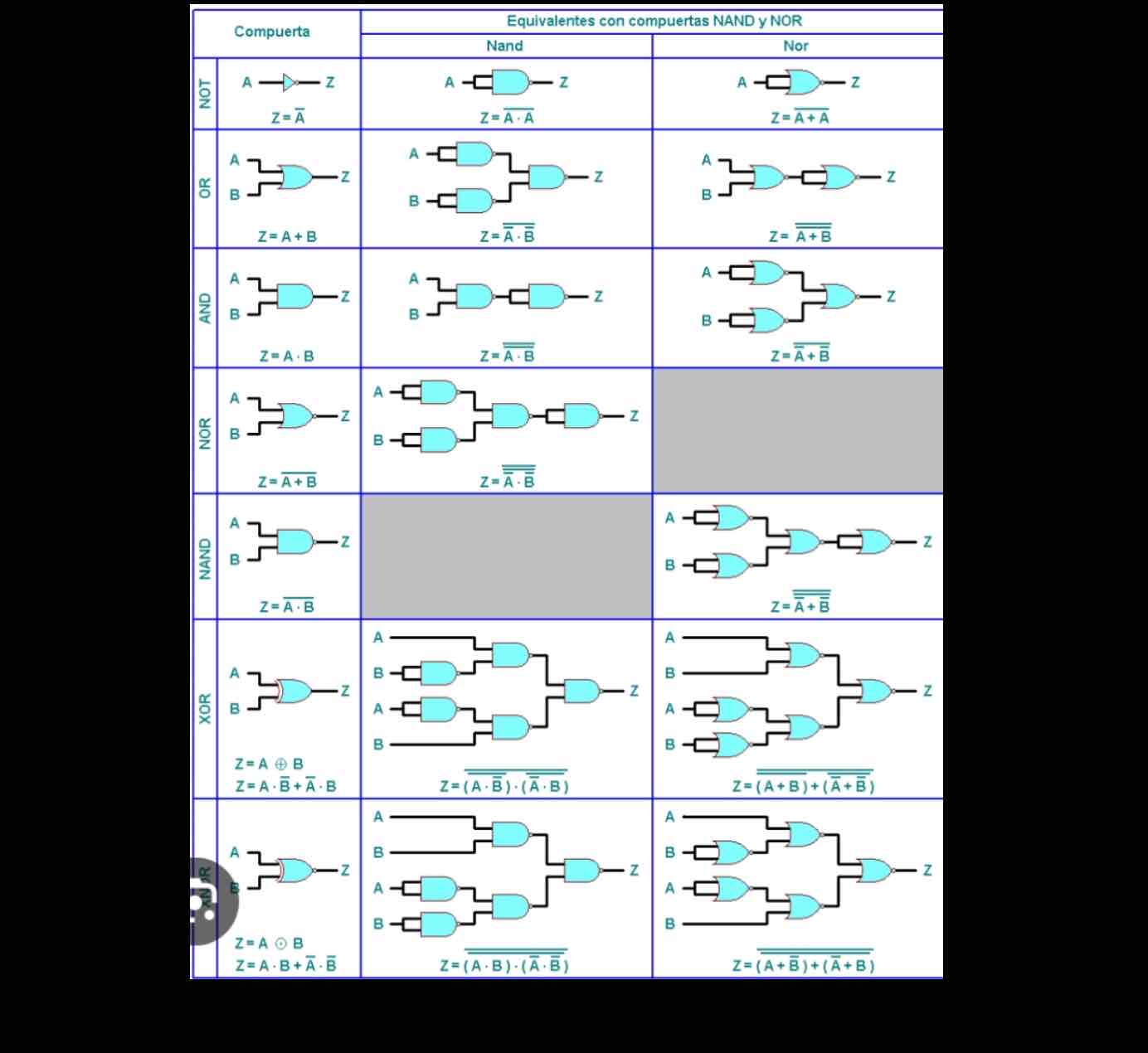

Conjuntos funcionalmente completos

AND,OR,NOT

AND,NOT

OR,NOT

NAND

NOR

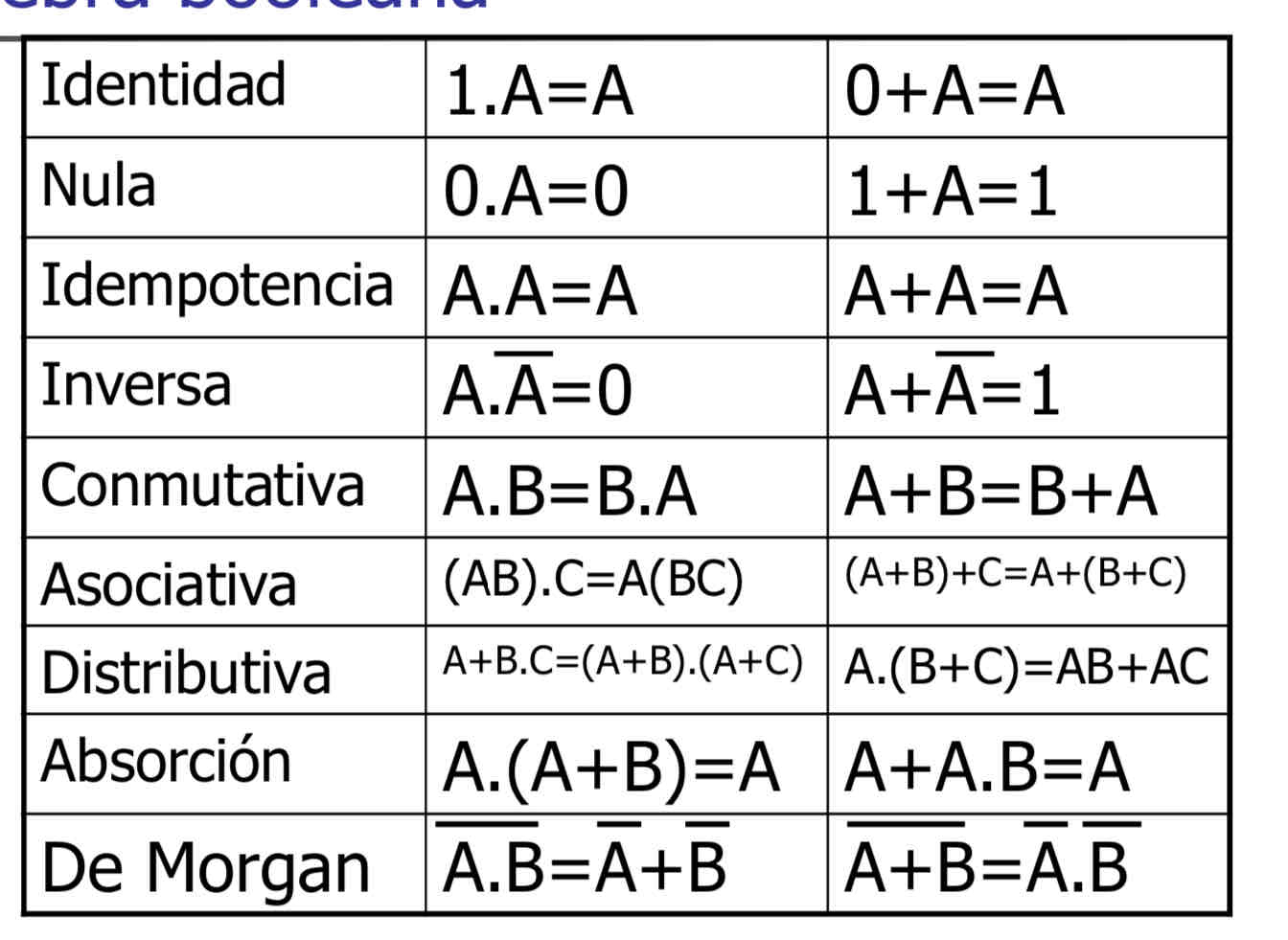

Álgebra de boole

Usa variables y operaciones lógicas. las variables toman dos posibles valores: 1 (V) o 0(F). Las op. lógicas básicas son: AND,OR y NOT.

Suma de productos (SoP) y un ejemplo

Expresar funciones booleanas detallando las combinaciones de los valores a,b y c que hacen que la función valga 1. EJ: f(a,b,c)= ~a*b*~c + ~a*b*c + a*b*~c

Productos de Suma (PoS) y un ejemplo

Expresar funciones booleanas detallando las combinaciones de los valores a,b y c que hacen que la función valga 0. EJ: (~a+b+c) * (~a+b+~c) * (a+b+~c)

Circuito digital

Compuertas

And= A.B

Or= A+ B

Not= Ā

Xor= A~B + ~AB

Nor= ~(A+B)

Identidades A.B

Equivalencias lógicas NAND y NOR

Circuito Combinatorio

Conjunto de puertas interconectadas cuya salida, en un momento dado, está determinada por los valores de las entradas en ese instante(si cambia la ENTRADA cambia la SALIDA, pero sus valores pasados no influyen en los valores de la SALIDA, ya que el C.C no tiene memoria)

ROM(Read Only Memory)

C.C y unidad de memoria en la que sólo se realiza la operación de lectura. Esto implica que la información binaria es permanente y se creó en el proceso de fabricación. Una ENTRADA dada a la ROM (línea de direcciones) produce siempre la misma salida (línea de datos).

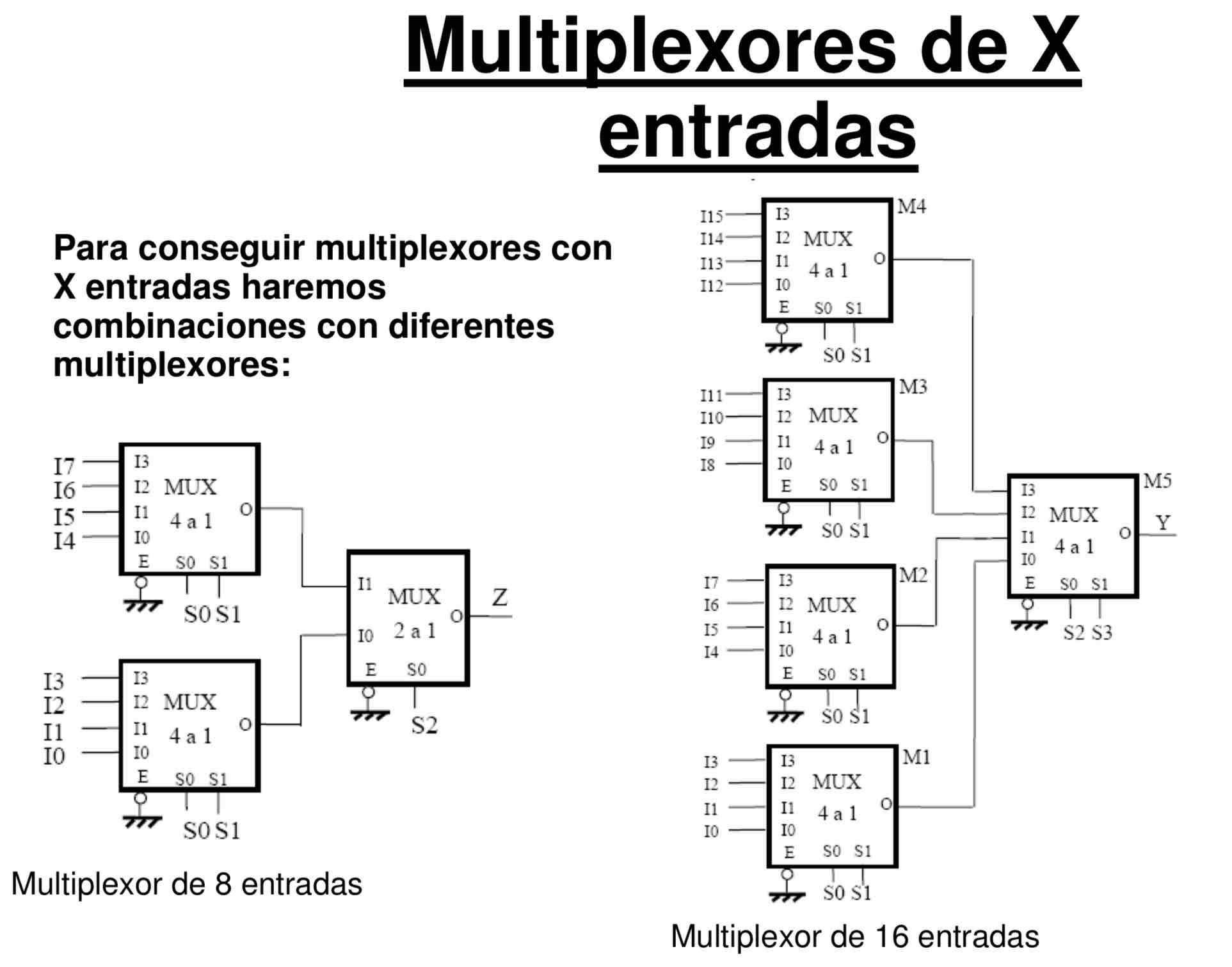

Multiplexor

Conecta varias ENTRADAS con una única SALIDA. En un momento dado se selecciona una de las ENTRADAS para que pase a la SALIDA. Se usan en circuitos digitales para controlar el enrutamiento de señales y datos. Consta de N entradas de datos (I0,I1,I2,…,In), M entradas de selección(S0,S1,…Sn), una única salida (F o Z) y un Enable (un solo bit que indica encendido o apagado)

2^n entradas= n selectores

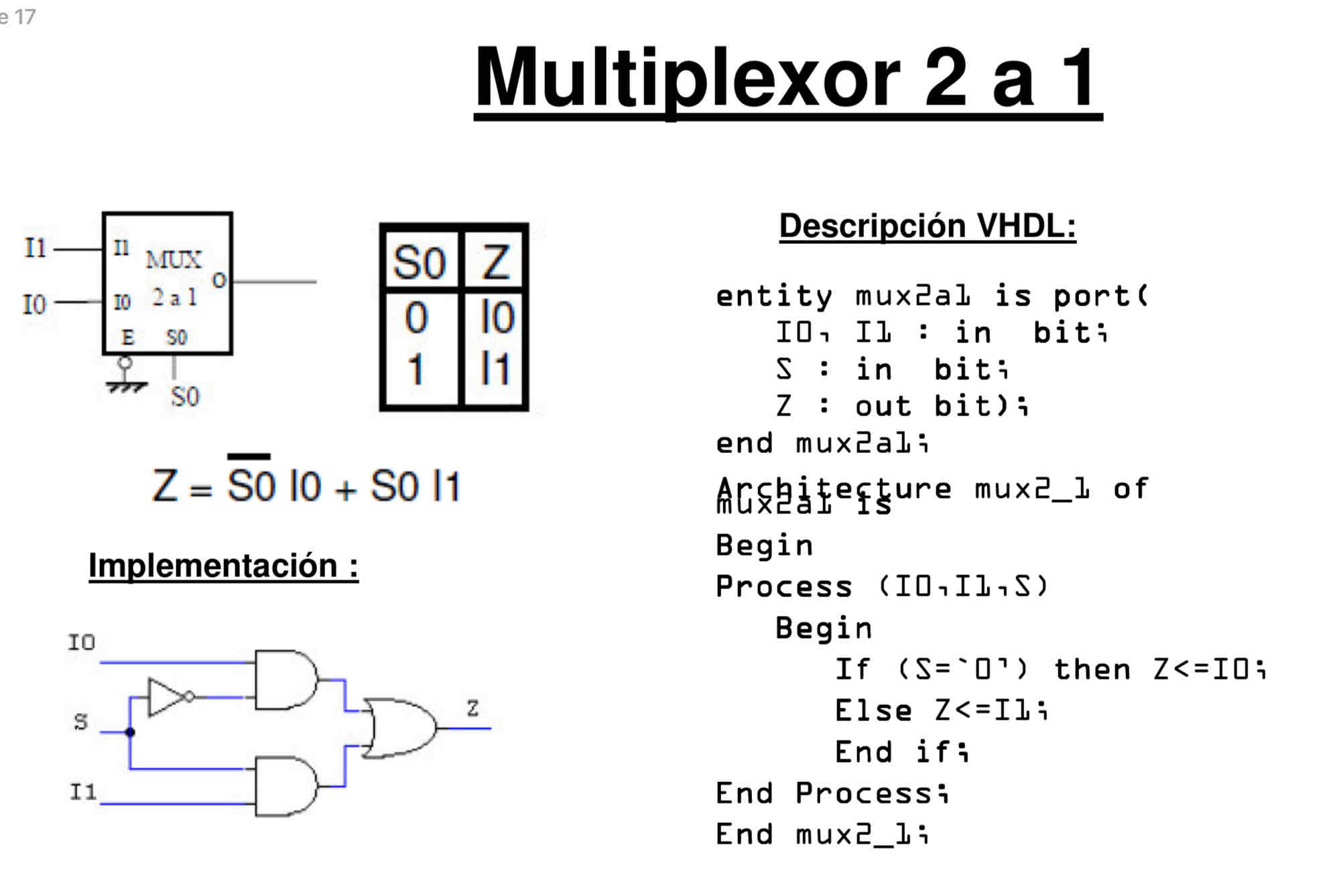

Multiplexor 2 a 1

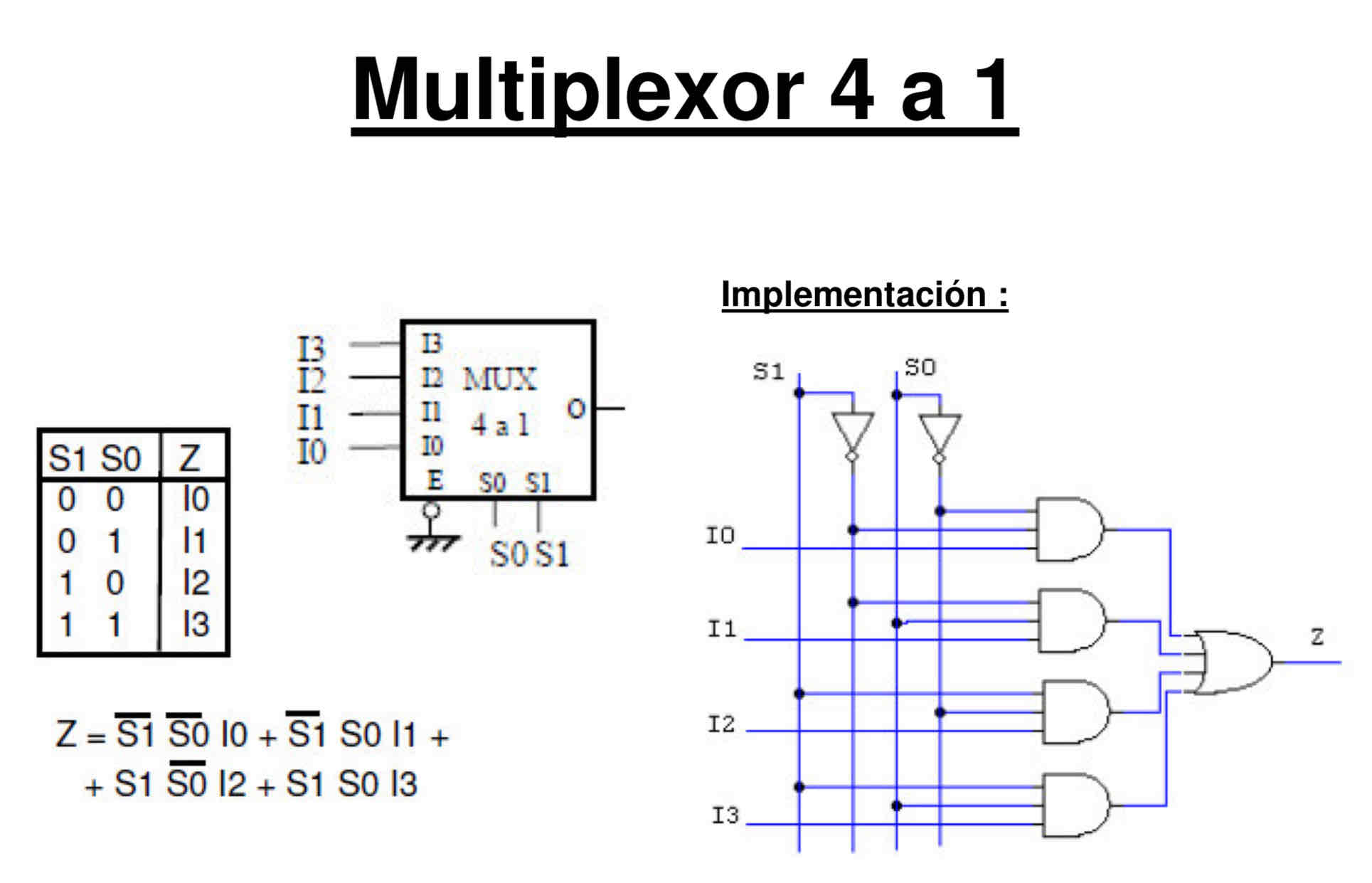

Multiplexor 4 a 1

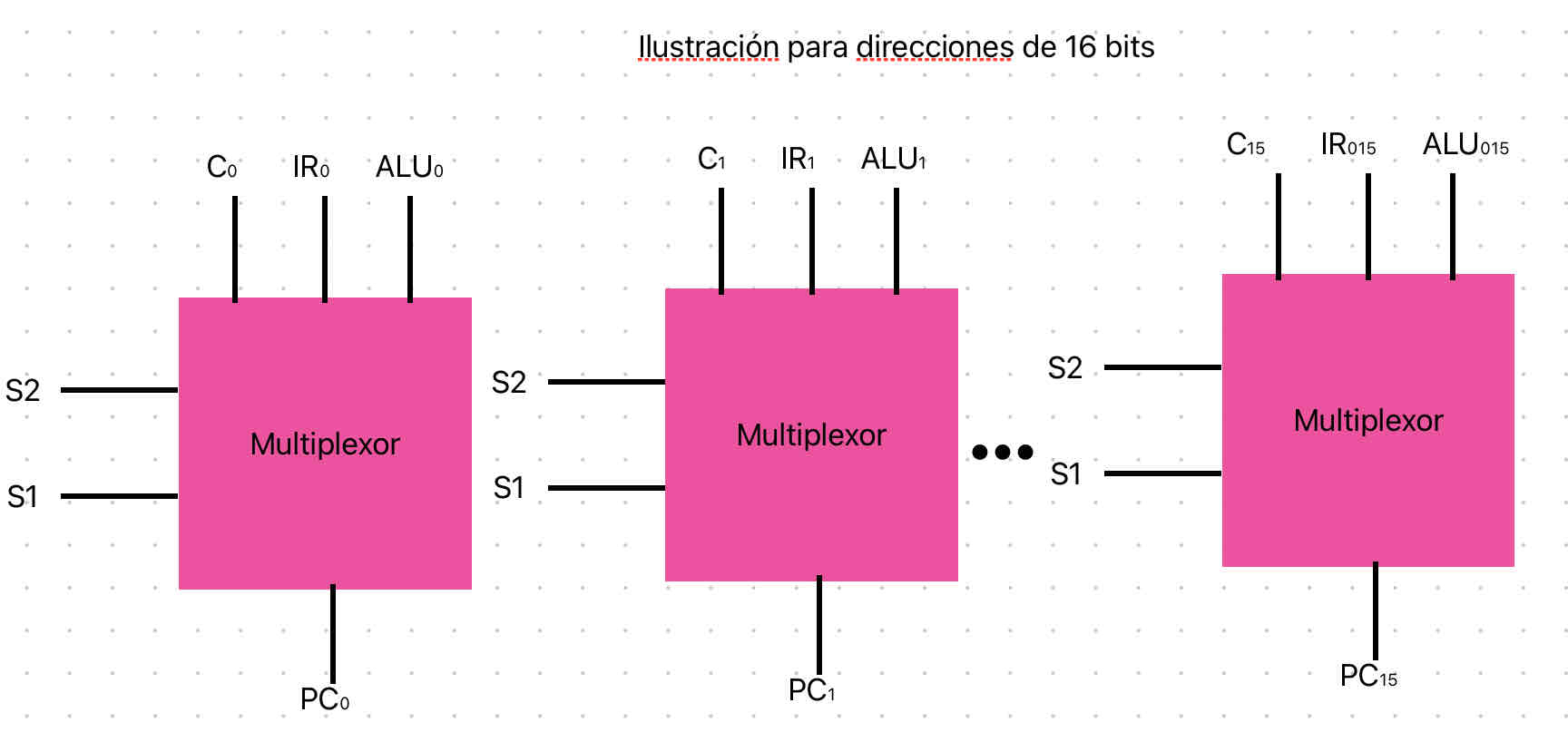

Uso del multiplexor ejemplo

Carga del contador de programa o PC (el valor debe venir de una o más fuentes distintas: de un contador binario, si el PC se va a incrementar para la siguiente instrucción; del registro de instrucciones (IR), si se acaba de ejecutar una instrucción de salto usando direccionamiento directo; de la salida de la ALU, si la instrucción de salto especifica la dirección usando modo de desplazamiento.

Las diferentes entradas se pueden conectar a las líneas de entrada de un multiplexor con el PC conectado a las líneas de salida. Y las líneas seleccionadas determinan cuál es el valor a cargar en el PC. Como el PC contiene varios bits, se usan varios multiplexores, uno por bit.

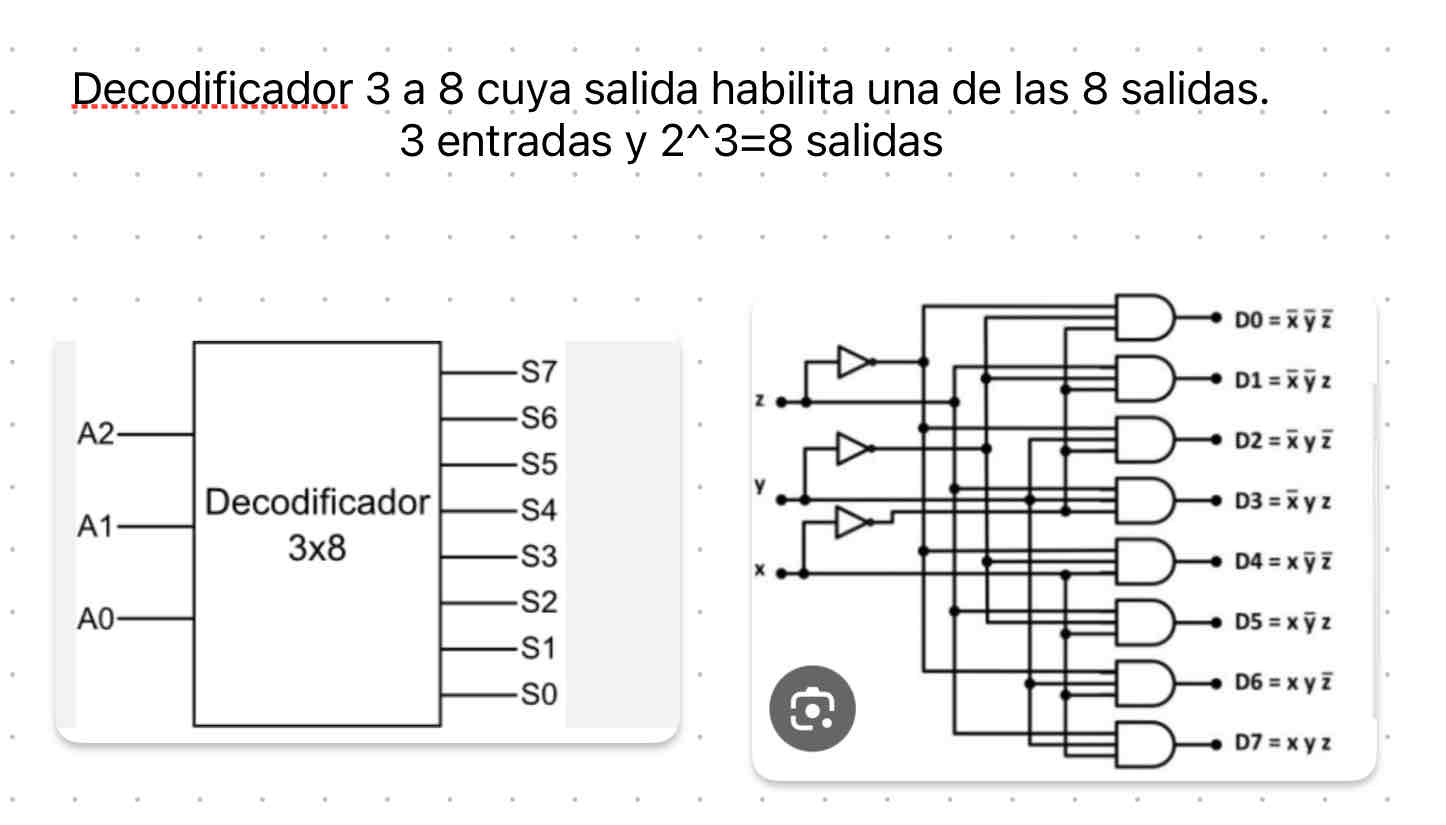

Decodificador

C.C con varias líneas de salida, con una sola de ellas seleccionada en un instante dado, dependiendo del patrón de líneas de entrada. En general tiene 2^n salidas y n entradas. Se usan por ejemplo en codificación de direcciones.

Demultiplexor

Tiene una línea adicional de entrada que el decodificador y conecta una única entrada a 1 o más salidas.

Decodificador 3 a 8

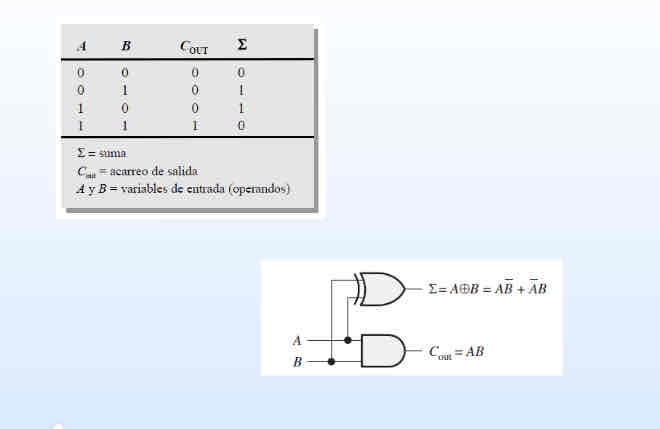

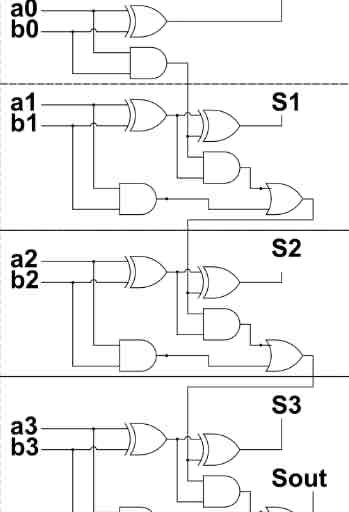

Half Adder o sumador completo

Suma dos digitos binarios simples A y B denominados sumandos y sus salidas son S (suma) y Acarreo (C out). La señal de acarreo representa un desbordamiento en el siguiente digito en una adición de varios dígitos

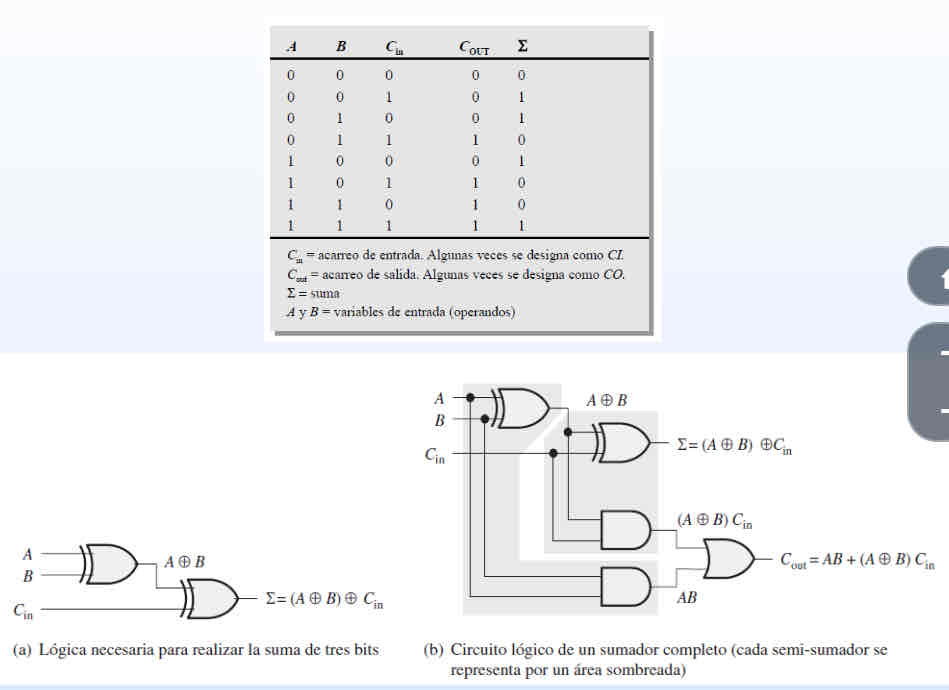

Full adder o sumador completo

Suma números binarios junto con las cantidades de acarreo. Un sumador completo de un bit añade 3 bits, a menudo escritos como A, B, C in; siendo A y B los sumandos y Cin el acarreo que proviene de la etapa anterior menos significativa. El full adder suele ser componente de una cascada de sumadores que suman 8,16,32,…. Números binarios de bits. El circuito produce una salida de dos bits (S y Cout) al igual que el half adder.

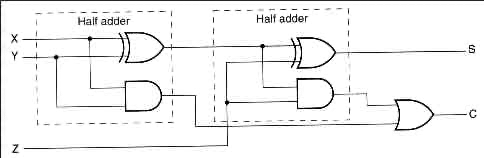

Full adder a partir de dos half adder

Sumador en serie de 4 bits

Circuitos secuenciales

Son un conjuntos de puertas lógicas interconectadas entre si, en el cual la salida en cualquier instante de tiempo T depende de las entradas en ese instante y del valor de las entradas en T -1

C.S Asincrónicos

Pueden cambiar de estado en cualquier instante de tiempo. Con retardos asociados a las puertas lógicas , los cuales son intervalos de tiempo que representan la demora en la propagación de una señal a través de una puerta y afectan a la sincronización de los circuitos digitales.

C.S Sincrónicos

Solamente se perciben cambios de estados en instantes marcados por el reloj

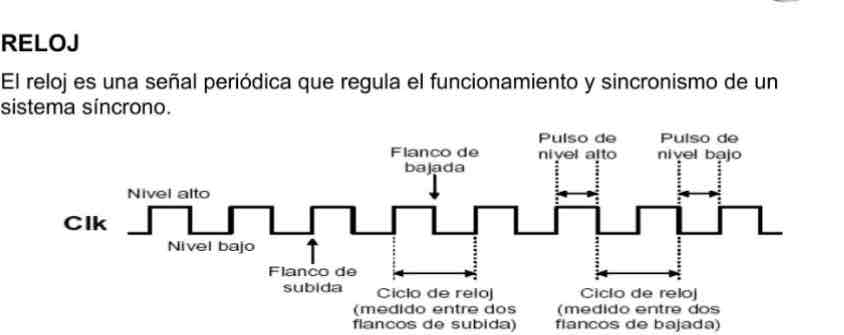

Reloj (Clock o CLK)

Señal de tiempo precisa que determina cuándo se producen eventos

Formas de representación de funciones booleanas

TABLA DE VERDAD: Para c/u de las 2^n combinaciones posibles de las n señales de entrada, se enumera el valor binario de c/u de las m señales de salida.

SÍMBOLO GRÁFICO: describe la organización de las interconexiones entre puertas.

ECUACIONES BOOLEANAS: c/ señal de salida se expresa como funciones booleanas de las señales de entrada.

Biestables

Forma más sencilla de un circuito secuencial, con la capacidad de permanecer en uno de dos estados posibles (0,1) durante un tiempo indefinido en ausencia de entrada, utilizando el principio de retroalimentación. Posee dos salidas que siempre son complementarias entre sí (Q y ~Q) y puede funcionar como memoria de 1 bit.

Tipos de sincronismo

POR FLANCO ASCENDENTE: El sistema lee las entradas cuando el CLK está en nivel alto (1) o nivel bajo (0).

POR FLANCO: el sistema lee las entradas cuando se produce una transición de sus pulsos que puede ser por flanco de bajada (de 1 a 0) o por flanco de subida (de 0 a 1)

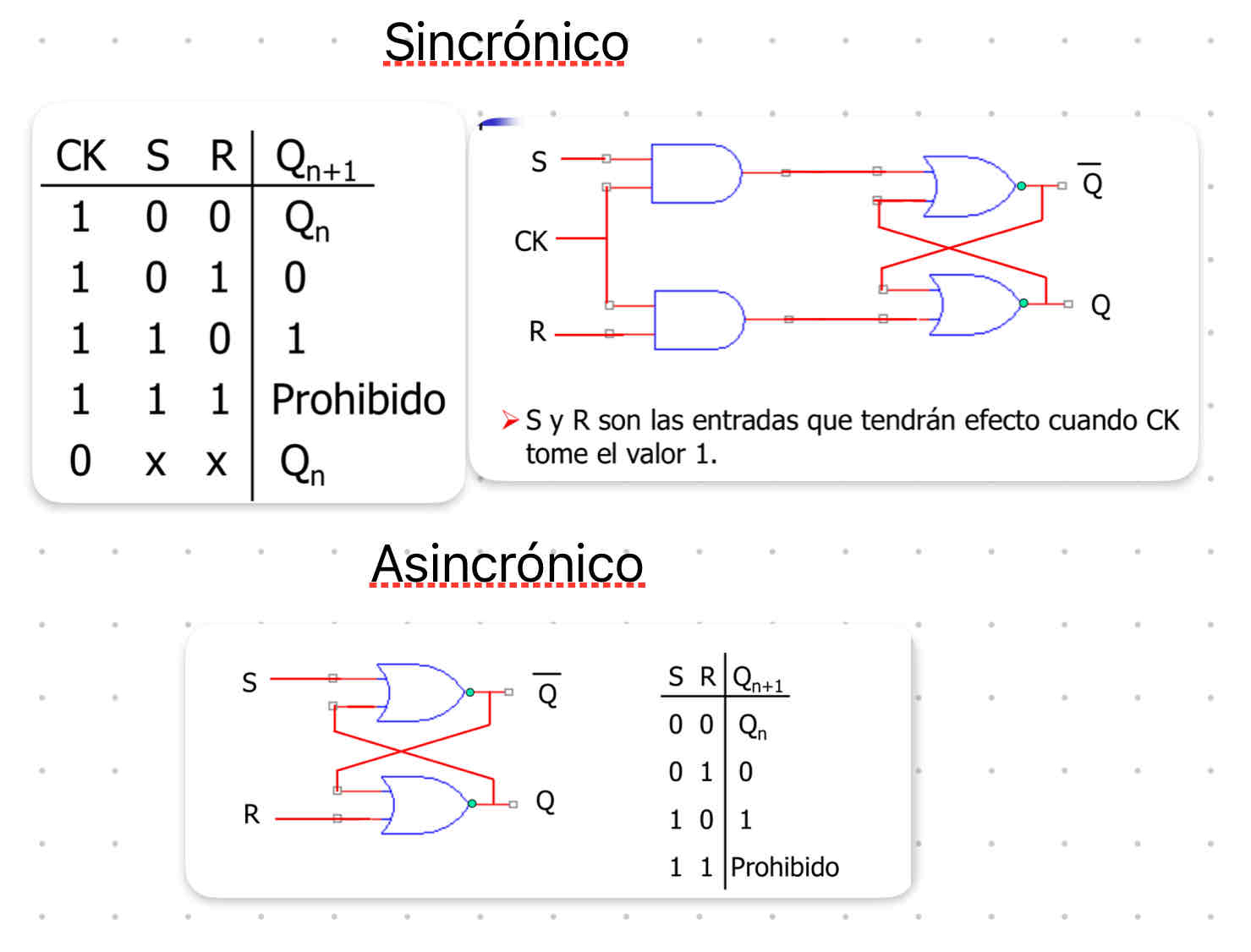

Biestable S-R

Circuito digital de 2 entradas: R(reset: cuando tiene valor 1 pone en 0 a la salida) y S(set: cuando tiene valor 1 pone en 1 a la salida). Cuando ambas tienen valor 0, la salida queda igual, pero si ambas valen 1, el biestable no sabe cómo actuar y la salida puede seguir igual o cambiar aleatoriamente, es decir falla (se conoce como entrada prohibida). Existen dos tipos el sincrónico y el asincrónico.

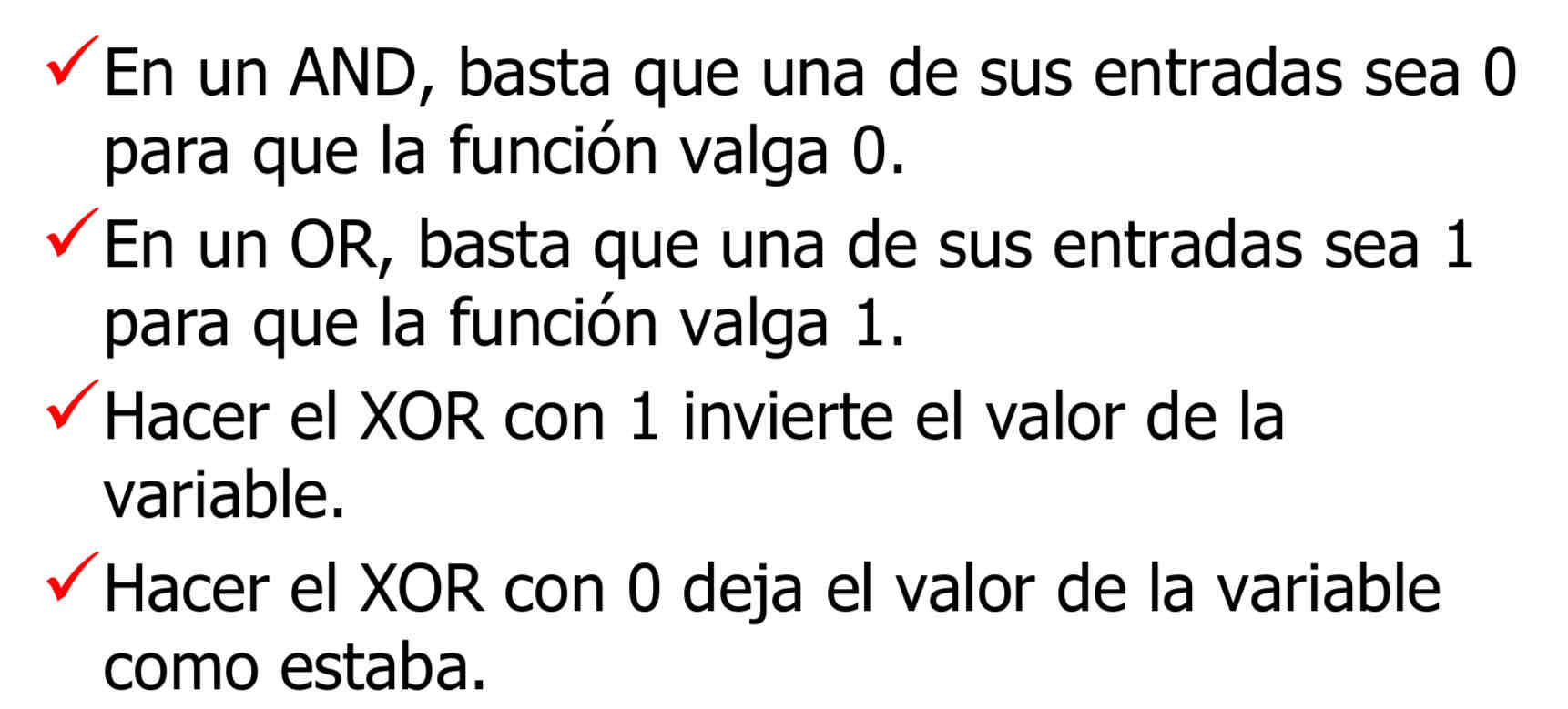

Mascaras y compuertas

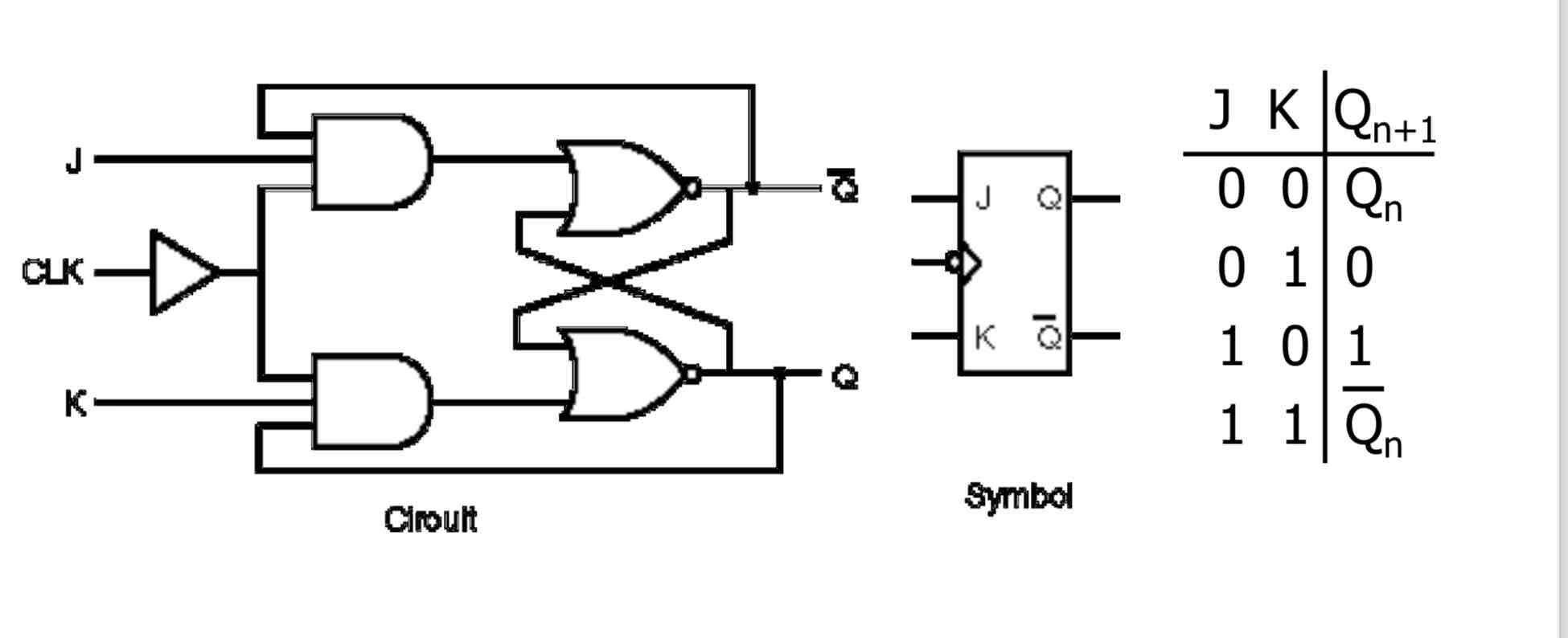

Biestable J-K

Diseñado para evitar el problema de indeterminación S-R cuando ambas entradas valen 1. En este biestable J es el equivalente a S y K el equivalente a R. Cuando ambas valen 1 se conmuta, es decir, la salida se invierte.

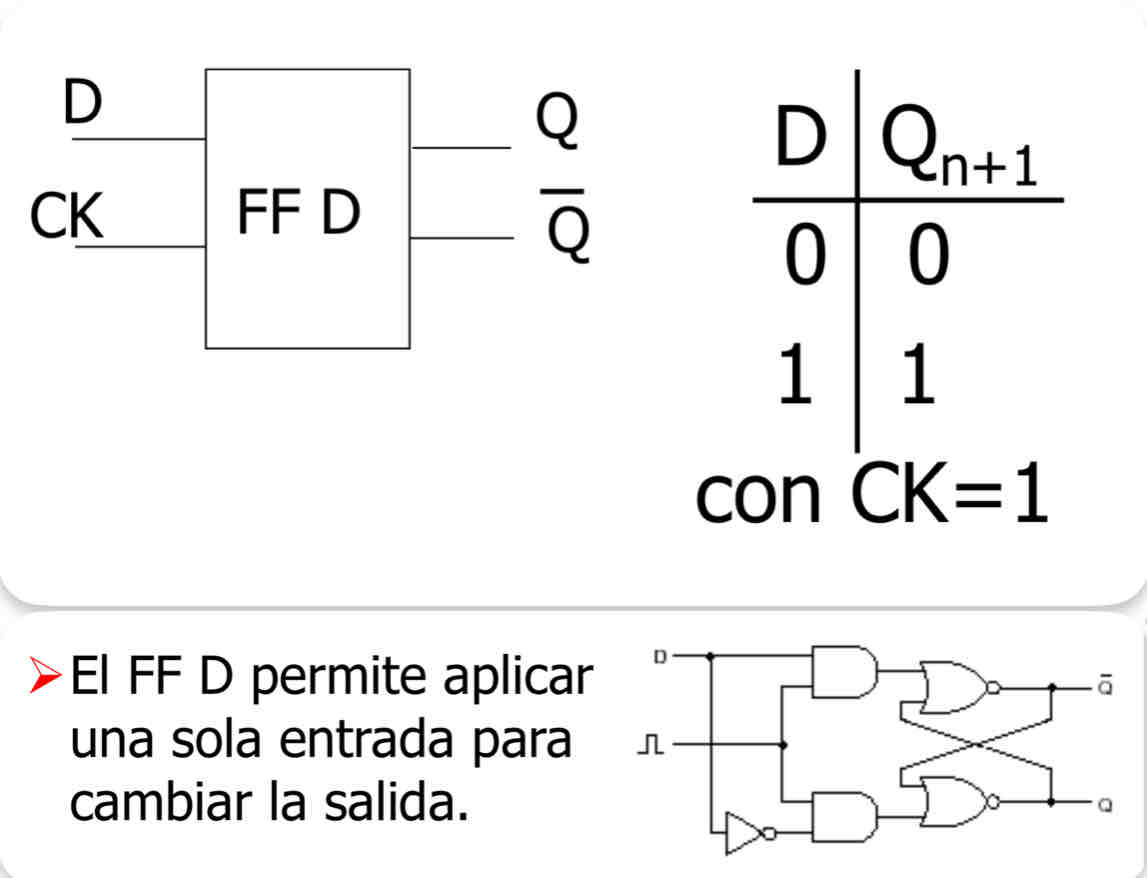

Biestable de datos o D

Sirve para almacenar 1 bit de datos. Posee 1 sola entrada llamada D(datos) y dos salidas complementarias Q y ~Q. Obtiene el valor de la entrada D cuando la señal de CLK se encuentra activada

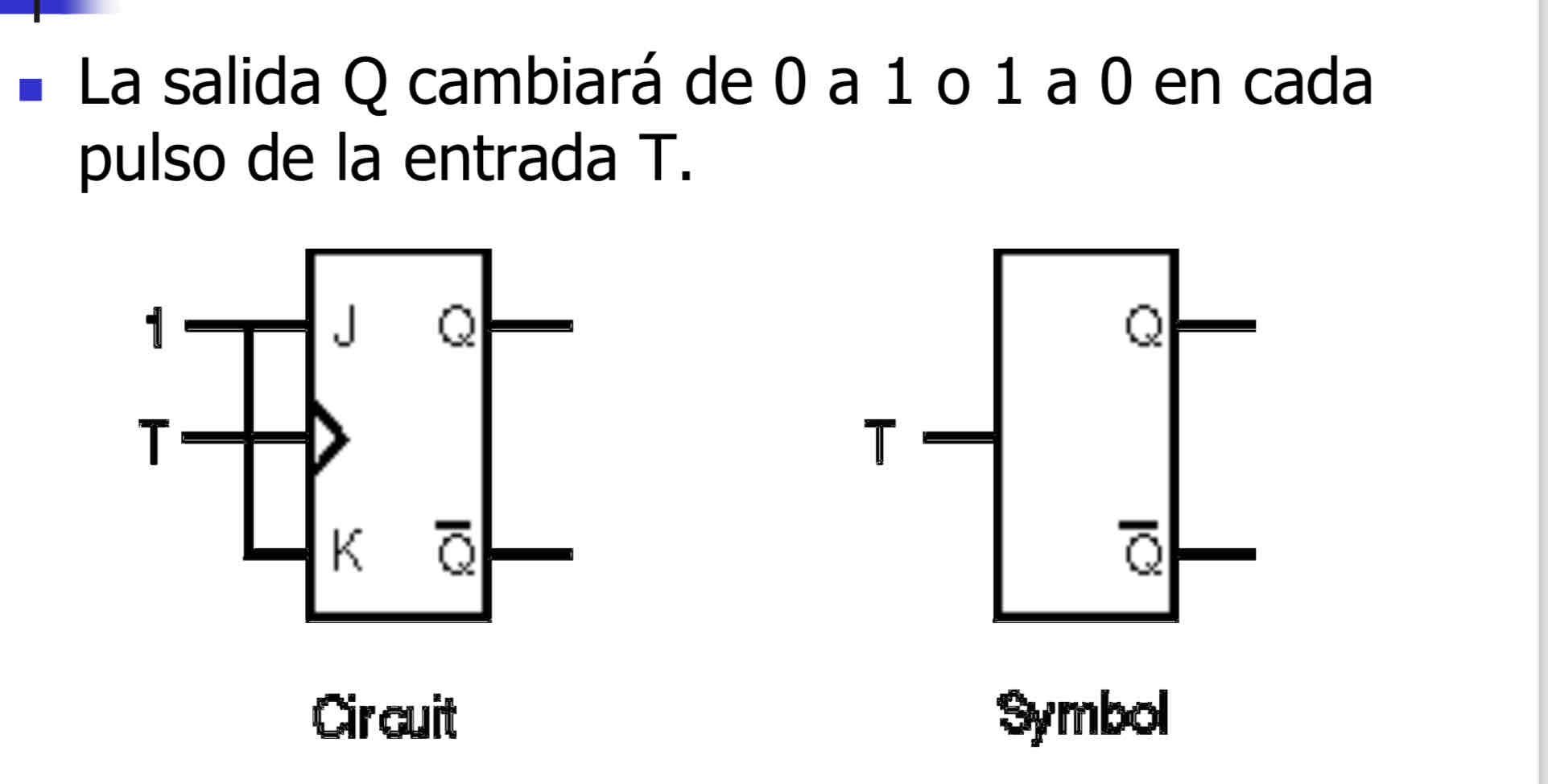

Toggle o T

La salida Q cambia de 0 a 1 (o de 1 a 0) en c/pulso de entrada T.

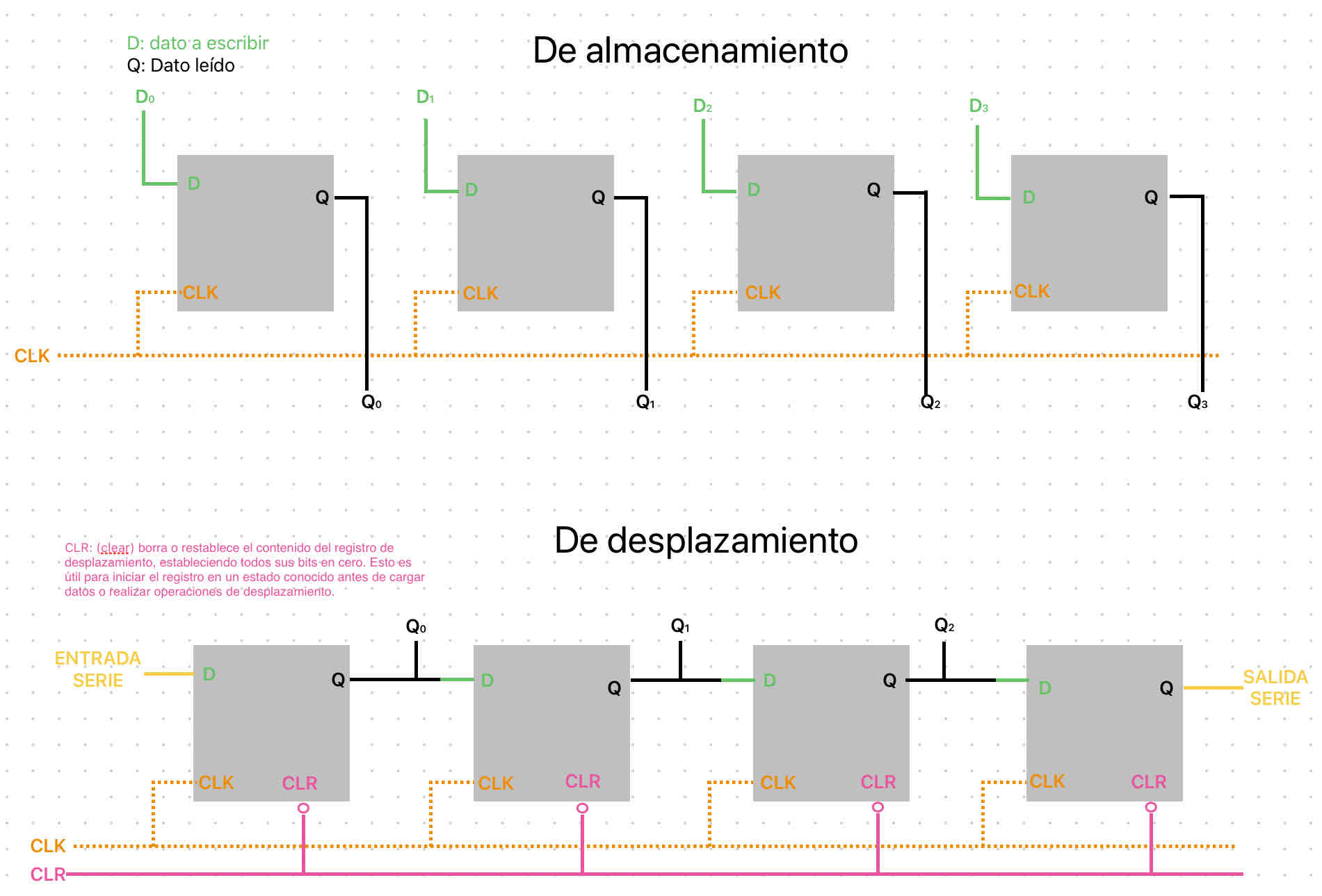

Registros

Se forman a partir de biestables D conectados en cascada. Un registro con n biestables es capaz de almacenar n bits. Son sincrónicos y todos los biestables están gobernados por la misma señal de reloj (CLK).

Dos tipos

A) De almacenamiento: Conjunto de biestables que se pueden leer o escribir simultáneamente

B)De desplazamiento (cuando se activan se desplazan los bits a la izq o a la derecha. Esto puede ser de Entrada/Salida serie (E/S 1 bit en c/ pulso de reloj) o Entrada/Salida paralelo: E/S todos los bits del dato en el mismo pulso

En la foto se ejemplifica registro de 4 bits.

Contadores

Estos se implementan utilizando n biestables T.

Hay 3 tipos:

A) Asincrónicos: Solo biestables sin puertas lógicas adicionales. La entrada de reloj solo se conecta al 1er biestable (el de menor peso). Las salidas (Q y ~Q) de c/biestable se conecta con el siguiente. Las entrada de datos de los biestables (J-K o T) se conectan con un 1 fijo.

B)Sincrónicos: La señal de CLK se conecta a todos los biestables, por lo tanto se activan simultáneamente. Las entradas de CLK al contador se conecta a las entradas de CLK de todos los biestables. La entrada de datos (J-K o T) del biestable de menor peso se conecta con un 1 fijo. Se precisan puertas adicionales para implementar la lógica que indique cuándo deben voltear su estado los biestables.

C) Módulo N: Nro de cuentas distintas que realiza dicho contador. Se elige un contador con n bits (ascendente o descendente) siendo 2^n-1 < n < 2^n y se eliminan las cuentas sobrantes