Week 8 P1 - Pipelining

0.0(0)

Card Sorting

1/17

There's no tags or description

Looks like no tags are added yet.

Study Analytics

Name | Mastery | Learn | Test | Matching | Spaced |

|---|

No study sessions yet.

18 Terms

1

New cards

What is latency ?

time to complete execution of one instruction

2

New cards

What is throughput for instructions in pipelining?

how many instructions completed per second

3

New cards

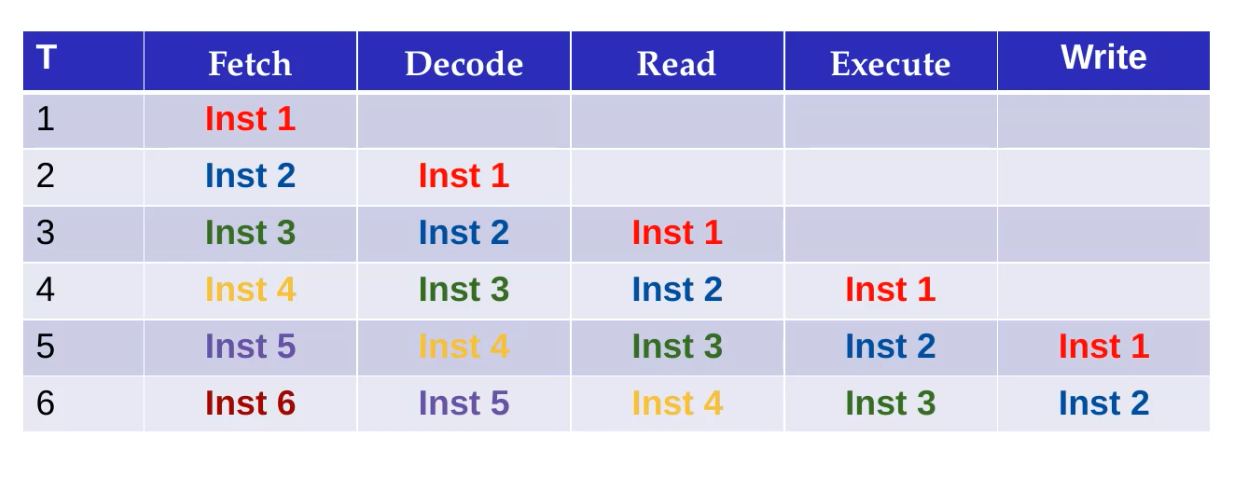

What is pipelining ?

A technique that **improves the performance** of tasks that involve many operations

4

New cards

How does pipelining work?

It **overlaps** the execution of one instruction with fetching the next instruction

5

New cards

What are pipeline latches ?

pipeline latches accept the output of each stage of each clock tick

they are simply memory circuits

they are simply memory circuits

6

New cards

What does throughout improve?

one instruction completes on every cycle so we can complete one instruction per cycle

7

New cards

What does pipelining do to the processors cycle time?

reduces it since the stages are simpler

8

New cards

Why does pipelining increase the latency?

increases the latency to the sum of all pipeline latches latencies so more instructions are completed

9

New cards

What are the three types of hazards in pipelining ?

**data hazards →** read after read read after write ..

**control hazards → branch instructions**

**structural hazards - > resources conflicts**

**control hazards → branch instructions**

**structural hazards - > resources conflicts**

10

New cards

what is a pipeline stall or “bubble”?

a stage in the pipeline that cannot perform any useful work due to the lack of data from an earlier stage.

11

New cards

what is result forwarding or result bypassing?

Allows the result of instructions to be passed between pipeline stages before being written into a register.

\

reduces the number of stalls in the pipeline

\

reduces the number of stalls in the pipeline

12

New cards

What is a conditional branch?

create dependencies since the branch instruction decides which instruction will execute next - a control hazard

13

New cards

When does a branch delay happen?

occurs between a branch instruction entering the pipeline , and the next instruction entering the pipeline

14

New cards

What is a pipeline stall / flush?

procedure enacted by a CPU when it cannot ensure that it will correctly process its instruction pipeline in the next clock cycle.

15

New cards

What is branch prediction?

CPU guesses which branch will be taken

if right - commit the result

if wrong --- flush pipeline

if right - commit the result

if wrong --- flush pipeline

16

New cards

What is speculative execution?

Execute both possible paths through code

when branch result known , commit one set of results to registers and discard the others

when branch result known , commit one set of results to registers and discard the others

17

New cards

A CPU with s ingle pipeline is a ___

Modern CPUs are ____

Modern CPUs are ____

scalar

superscalar

superscalar

18

New cards

Making a decision based on the results of an earlier instruction while it is being executed is called a:

\

Structural hazard

Data hazard

Control hazard

Pipeflush

\

Structural hazard

Data hazard

Control hazard

Pipeflush

data hazard