Understanding the Fetch-Execute Cycle in Computing

1/43

There's no tags or description

Looks like no tags are added yet.

Name | Mastery | Learn | Test | Matching | Spaced | Call with Kai |

|---|

No study sessions yet.

44 Terms

Fetch-execute cycle

The process by which a computer retrieves an instruction from memory, decodes it, and executes it.

Arithmetic and Logic Unit (ALU)

A component of the processor that performs arithmetic and logical operations.

Control Unit

The part of the processor that directs the operation of the processor and coordinates how data moves around.

Registers

Small, high-speed storage locations within the CPU used to hold temporary data and instructions.

Program Counter (PC)

A special register that stores the address of the next instruction to be fetched, decoded, and executed.

Accumulator (ACC)

A register that temporarily holds the results of arithmetic and logic operations.

Memory Address Register (MAR)

A register that holds the address of the memory location of the data/instruction to be accessed.

Memory Data Register (MDR)

A register that temporarily stores the data/instruction to be used.

Current Instruction Register (CIR)

A register that holds the instruction currently being decoded or executed.

Buses

Communication systems that transfer data between components inside a computer, including data, address, and control buses.

Von Neumann Architecture

A computer architecture where programs and data are stored together in the same memory, using a single processor for linear processing of instructions.

Fetch-Decode-Execute Cycle

The sequence of steps a computer takes to retrieve an instruction from memory, decode it, and execute it.

Opcode

The part of an instruction that specifies the operation to be performed.

Operand

The data or location (memory address or register) on which the opcode operates.

Special Registers

Registers specifically used to carry out the fetch-decode-execute sequence of instructions.

System Bus

A communication pathway that connects the CPU to other components of the computer.

Instruction

A binary coded operation that the CPU can execute.

Data

Information processed or stored by a computer.

Control

Signals that manage the operations of the CPU and other components.

Memory

The component of a computer that stores data and instructions.

Clock

A timing device that synchronizes the operations of the computer's components.

Fetch-Execute Cycle Animation

A visual representation of the fetch-execute cycle process.

State of the PC

The address held in the Program Counter during the fetch/execute cycle.

Opcode

This part of the instruction indicates the specific operation or action that the CPU should perform like addition, subtraction, or loading data from memory.

Accumulator

(temporarily) stores intermediate results (in the ALU), holds the data currently being processed, and the result of calculation is held in accumulator before being passed to memory unit.

Instruction cycle

The sequence of steps that a processor follows to execute an instruction, including fetching, decoding, and executing the instruction.

Fetch-execute cycle

Processors operate in defined stages that are used to carry out program instructions, repeated for each instruction in a program.

Program Counter (PC)

Holds the address of the next instruction to be carried out.

Memory Address Register (MAR)

Holds the address of the memory location to be accessed.

Memory Data Register (MDR)

Holds the data that is being transferred to or from memory.

Current Instruction Register (CIR)

Holds the instruction that is currently being executed.

Control Unit

Interprets the operation code so that the CPU knows what to do.

Fetch Phase

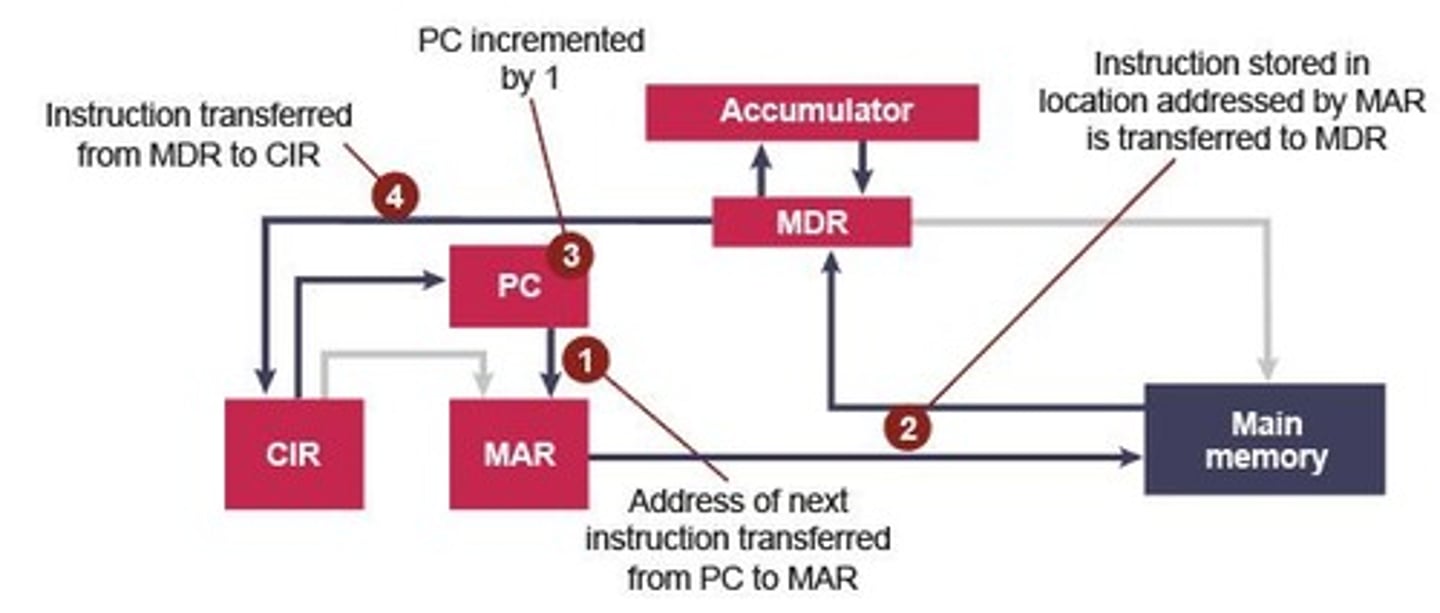

The phase where the program counter holds the address of the next instruction, which is copied to the MAR.

Decode Phase

The phase where the contents of the CIR are decoded into binary and the operation code is interpreted.

Execute Phase

The phase where the instruction is executed and the result is held in the accumulator or stored in memory.

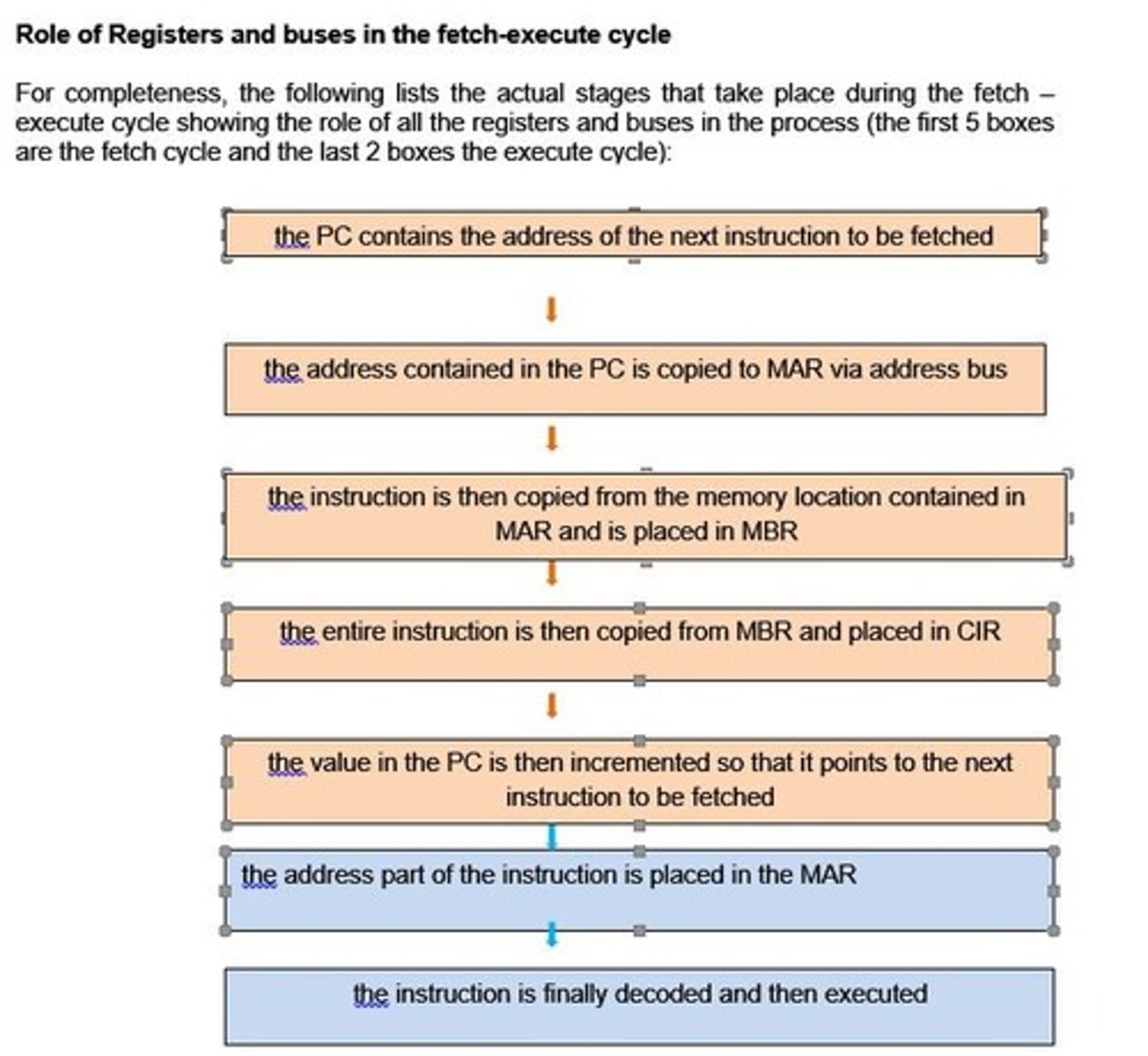

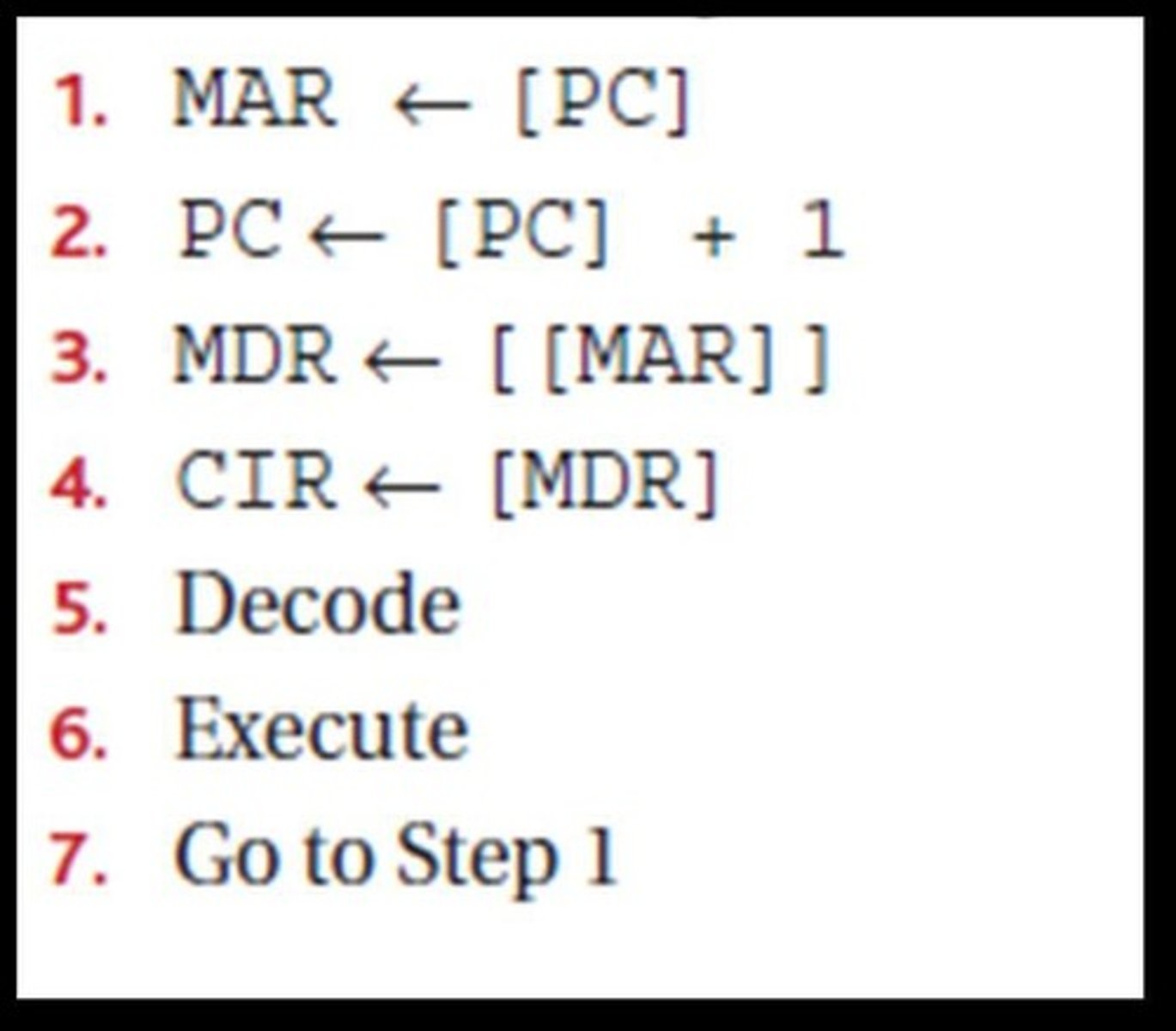

Fetch: Steps 1 - 4

1. The address of the next instruction is copied from the PC to the MAR. 2. The instruction held at that address is copied to the MDR. 3. The contents of the PC are incremented. 4. The contents of the MDR are copied to the CIR.

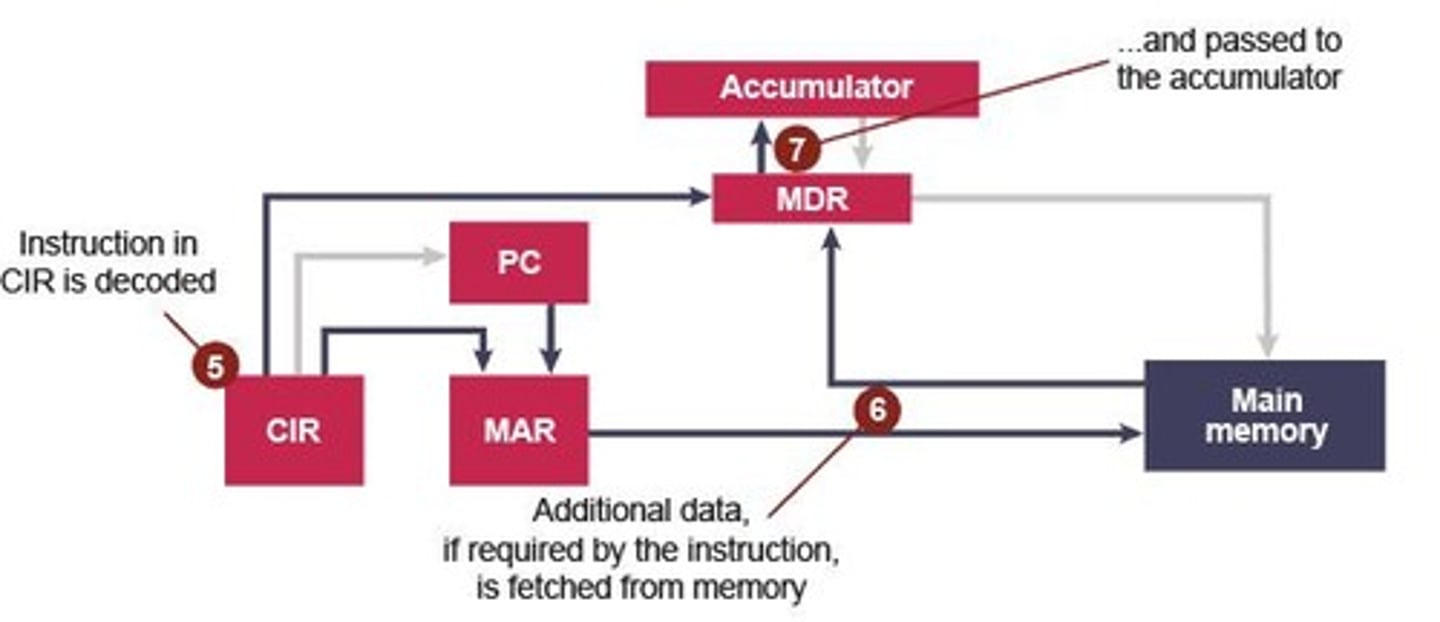

Decode: Steps 5 - 7

5. The instruction held in the CIR is decoded. 6. It is split into operand and opcode. 7. Additional data, if required, is fetched from memory and passed to the accumulator.

Register Transfer Notation

A method of describing the transfer of data between registers in a CPU.

Fetch Execute Cycle Summary

1. Value stored in PC is placed in MAR. 2. PC is incremented. 3. Memory accessed for location held in MAR. 4. Contents of that location placed in MDR/MBR. 5. Contents of MDR/MBR placed in CIR. 6. Operation code held in CIR is decoded. 7. Address held in CIR is copied from CIR to MAR. 8. Contents of address held in MAR are copied to MDR/MBR/sent to accumulator.

Clock Pulse

Used to control stages of the fetch-execute cycle.

Effective Address

The address from which data is to be read or written, determined during the decode phase.

Operand

Holds either the address of the data to be used or the actual data to be operated on.

Indirect Address

An addressing mode where the address of the data is not given directly but is stored in another location.

Arithmetic Operation

Operations such as addition, subtraction, multiplication, and division that are performed by the ALU.