A- Level OCR Computer Science - Types of Processors

1/3

Name | Mastery | Learn | Test | Matching | Spaced | Call with Kai |

|---|

No analytics yet

Send a link to your students to track their progress

4 Terms

Issues in von Neumann architecture

Data and programs share the same memory

A program may overwrite data with programming instructions if not written carefully

Program instructions may also be overwritten with data

Programs and data share the same bus = slower processing due to traffic

Word size for programs and data are the same

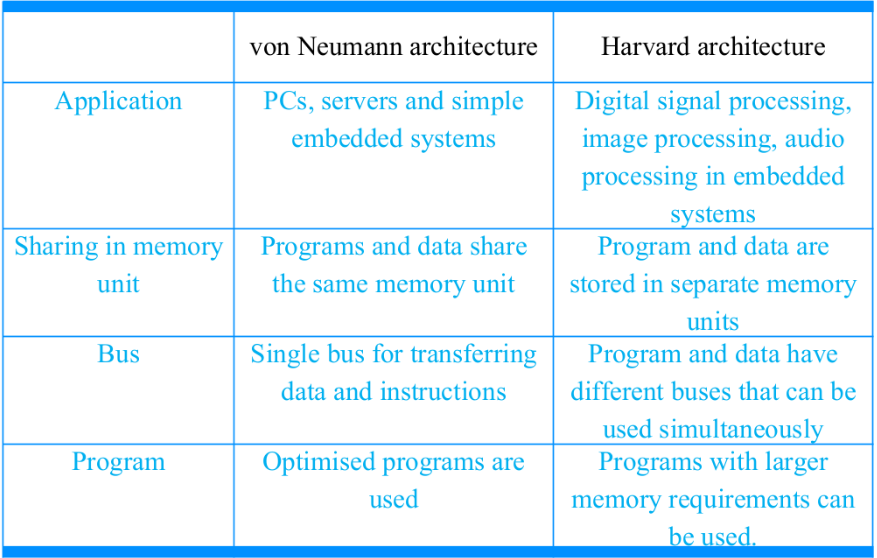

Harvard architecture

Harvard architecture uses two separate memory space for data and program

This means that Harvard architecture use a separate buses for each memory space

Programs and data can be processed simultaneously = better processing speed

No chance of overwritten data

Characteristics of program memory and data memory may be different

von Neumann architecture vs. Harvard architecture

Modern Computer Architecture

Both types of architecture are used in modern computers.

The main memory follows the von Neumann architecture

Whereas, the cache memory follows the Harvard architecture

Advanced digital signal processors provide multiple buses for data transmission with separate buses for read and write operations.