CPSC355 Final

0.0(0)

Studied by 4 peopleCard Sorting

1/143

Earn XP

Description and Tags

Last updated 8:53 PM on 12/11/22

Name | Mastery | Learn | Test | Matching | Spaced | Call with Kai |

|---|

No analytics yet

Send a link to your students to track their progress

144 Terms

1

New cards

CPU, System clock, primary memory, secondary memory, peripheral input and output devices, bus

Basic components of a computer

2

New cards

CPU

the brain of the computer.

- executes instructions

- controls the transfer of data across the bus

- usually contained on a single microprocessor chip

- executes instructions

- controls the transfer of data across the bus

- usually contained on a single microprocessor chip

3

New cards

Control unit, Arithmetic logic unit, registers

3 main parts of the CPU

4

New cards

control unit (CU)

Directs the execution of instructions

1. Loads an operation code (opcode) from primary memory into the Instruction Register (IR) via the bus ("the fetch")

2. Decodes the opcode to identify the operation

3. If necessary, transfers data between primary memory and registers

4. If necessary, directs the ALU to operate on data in registers

1. Loads an operation code (opcode) from primary memory into the Instruction Register (IR) via the bus ("the fetch")

2. Decodes the opcode to identify the operation

3. If necessary, transfers data between primary memory and registers

4. If necessary, directs the ALU to operate on data in registers

5

New cards

arithmetic logic unit (ALU)

Performs arithmetic and logical operations on data stored in registers

- Eg: add numbers in 2 source registers, and store the result in a destination register

- Eg: Do a bitwise AND using data in 2 registers

- Eg: add numbers in 2 source registers, and store the result in a destination register

- Eg: Do a bitwise AND using data in 2 registers

6

New cards

Registers

Binary storage units within the CPU

- May contain:

- Data

- Addresses (locations in integers)

- Instructions

- Status information

- May contain:

- Data

- Addresses (locations in integers)

- Instructions

- Status information

7

New cards

The System Clock

Generates a clock signal to synchronize the CPU and other clocked devices

- Is a square wave at a particular frequency (0-3.3 to 5 volts)

- Devices coordinate on the rising or falling edges

- Is a square wave at a particular frequency (0-3.3 to 5 volts)

- Devices coordinate on the rising or falling edges

8

New cards

Primary Memory

AKA RAM

- Any byte in memory can be accessed directly if you know its address

- Can be written to and read from

- Volatile: data disappears after the device is powered off

- Is used to store program instructions and program data (variables)

- Consists of a sequence of addressable memory locations, each location is typically one byte long

- Any byte in memory can be accessed directly if you know its address

- Can be written to and read from

- Volatile: data disappears after the device is powered off

- Is used to store program instructions and program data (variables)

- Consists of a sequence of addressable memory locations, each location is typically one byte long

9

New cards

Von Neumann

In _____________ architecture, RAM contains both data and programs (instructions)

10

New cards

Harvard

In _____________ architecture, there are separate memories for data and for programs (instructions)

11

New cards

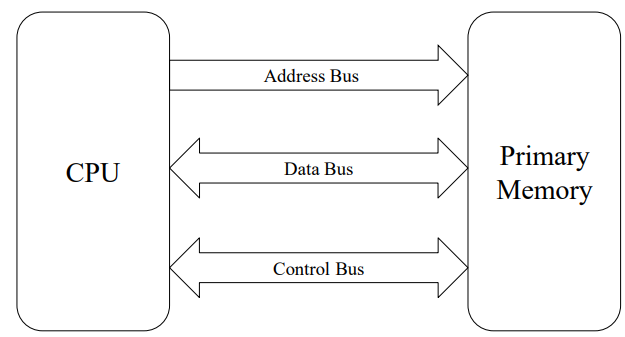

bus

A set of parallel data/signal lines used to transfer info between computer components

- Often subdivided into address, data and control busses

- Often subdivided into address, data and control busses

12

New cards

Address Bus

- Specifies a memory location in RAM

- From CPU to primary memory

- Or sometimes a memory mapped I/O device

- From CPU to primary memory

- Or sometimes a memory mapped I/O device

13

New cards

Data Bus

Used for bidirectional data transfer

14

New cards

Control Bus

Used to control or monitor any devices connected to the bus

- E.g, the read/write signal for RAM

- E.g, the read/write signal for RAM

15

New cards

Expansion bus

May be connected to the computer's local bus

- Makes it easy to connect additional I/O devices to the computer

- USB, SCSI, PCIe

- Makes it easy to connect additional I/O devices to the computer

- USB, SCSI, PCIe

16

New cards

Secondary Memory

Is used to hold a computer's file system- stores files containing programs or data

- Is non volatile read/write memory

- Usually an HDD, but sometimes SDD

- Is non volatile read/write memory

- Usually an HDD, but sometimes SDD

17

New cards

Peripheral I/O Devices

Allow communication between computer and the external environment

- Input: Keyboard, mouse, microphone

- Output: Speaker, monitor, printer

- I/O: HDD, modem

- Input: Keyboard, mouse, microphone

- Output: Speaker, monitor, printer

- I/O: HDD, modem

18

New cards

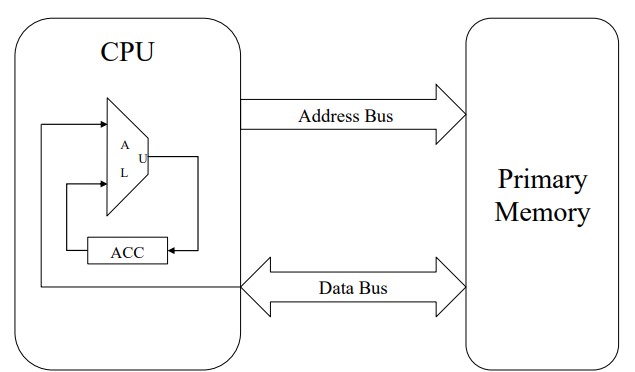

Accumulator, load/store

The 2 basic CPU architectures

19

New cards

Accumulator machine

Operands for an instruction come from the accumulator register (ACC) and from a single location in RAM

- ALU results are always put into the ACC

- The ACC can be loaded from or stored to RAM

- ALU results are always put into the ACC

- The ACC can be loaded from or stored to RAM

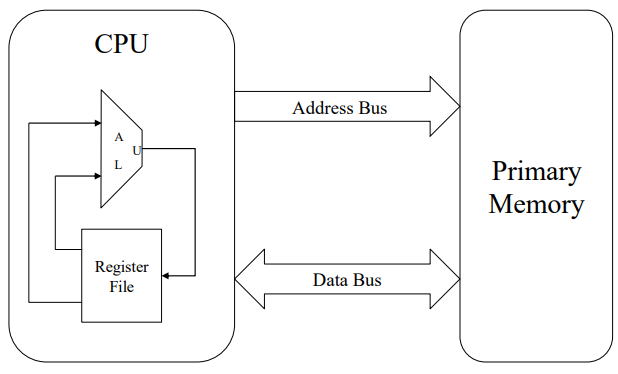

20

New cards

load/store machine

Only load and store instructions can access RAM

- Other instructions operate on specified registers in the register file, not on RAM

- Registers are more quickly accessed than RAM, so this is fast

- Typical program sequence:

1. Load registers from memory

2. Execute an instruction using two source registers, putting the result into a destination register

3. Store the result back into memory

- Other instructions operate on specified registers in the register file, not on RAM

- Registers are more quickly accessed than RAM, so this is fast

- Typical program sequence:

1. Load registers from memory

2. Execute an instruction using two source registers, putting the result into a destination register

3. Store the result back into memory

21

New cards

Reduced Instruction Set Computer (RISC)

Uses only simple instructions that can be executed in one machine cycle

+ Enables faster clock rates, thus faster overall execution

- Makes programs larger, more complex (e.g, the original SPARC had no mult, had to be done using repeated add-shift)

Machine instructions are always the same size

Makes decoding simpler and faster

- E.g, ARMv8 instructions are always 32 bits wide

+ Enables faster clock rates, thus faster overall execution

- Makes programs larger, more complex (e.g, the original SPARC had no mult, had to be done using repeated add-shift)

Machine instructions are always the same size

Makes decoding simpler and faster

- E.g, ARMv8 instructions are always 32 bits wide

22

New cards

Complex Instruction Set Computer (CISC)

May have instructions that take many cycles to execute + provided for programmer convenience

- Slows down overall execution speed

Machine instructions vary in length, and may be followed by "immediate" data

- Makes coding difficult and slow

- Slows down overall execution speed

Machine instructions vary in length, and may be followed by "immediate" data

- Makes coding difficult and slow

23

New cards

instruction cyle

The CPU executes each instruction in a series of small steps;

1. Fetch the instruction from memory into the instruction register (IR)

- The Program Counter register (PC) contains its address

2. Increment PC to point to the next instruction

3. Decode the instruction

4. If the instruction uses an operand in RAM, calculate its address. Repeat if necessary

5. Fetch the operand. Repeat if necessary

6. Execute the instruction

7. If the instruction produces a result that is stored in RAM, calculate its address. Repeat if necessary

8. Store the result. Repeat if necessary

1. Fetch the instruction from memory into the instruction register (IR)

- The Program Counter register (PC) contains its address

2. Increment PC to point to the next instruction

3. Decode the instruction

4. If the instruction uses an operand in RAM, calculate its address. Repeat if necessary

5. Fetch the operand. Repeat if necessary

6. Execute the instruction

7. If the instruction produces a result that is stored in RAM, calculate its address. Repeat if necessary

8. Store the result. Repeat if necessary

24

New cards

Opcode

The field that denotes the operation and format of an instruction.

25

New cards

Operand

An element that identifies the values to be used in a calculation.

26

New cards

Pseudo OPs (assembler directives)

do not generate machine instructions, but give the assembler extra information

- e.g .global start

- e.g .global start

27

New cards

El0

ARMv8 Exception Level:

For normal user applications with limited privileges

- Restricted access to a limited set of instructions and registers, and to certain parts of memory

- Most programs work at this level

For normal user applications with limited privileges

- Restricted access to a limited set of instructions and registers, and to certain parts of memory

- Most programs work at this level

28

New cards

El1

ARMv8 Exception Level:

For the OS kernel

- Privileged access to instructions, registers, and memory

- Accessed indirectly by user programs using system calls

For the OS kernel

- Privileged access to instructions, registers, and memory

- Accessed indirectly by user programs using system calls

29

New cards

El2

ARMv8 Exception Level:

- for a Hypervisor

- Support virtualization, where the computer hosts multiple guest operating systems, each on its own virtual machine

- for a Hypervisor

- Support virtualization, where the computer hosts multiple guest operating systems, each on its own virtual machine

30

New cards

El3

ARMv8 Exception Level:

- Includes the Secure Monitor

- Includes the Secure Monitor

31

New cards

31

Number of general purpose registers AArch64 has

32

New cards

X0-X7

Register purposes:

used to pass arguments into a procedure, and return results

used to pass arguments into a procedure, and return results

33

New cards

x8

Register purposes:

indirect result location register

- Used for returning structures

indirect result location register

- Used for returning structures

34

New cards

X9-X15

Register purposes:

temporary caller saved registers

temporary caller saved registers

35

New cards

x16, x17

Register purposes:

intra-procedure-call temporary registers (IP0, IP1)

intra-procedure-call temporary registers (IP0, IP1)

36

New cards

x18

Register purposes:

platform register

platform register

37

New cards

X29

Register purposes:

frame pointer (FP) register

frame pointer (FP) register

38

New cards

X30

Register purposes:

procedure link register (LR)

procedure link register (LR)

39

New cards

x19-x28

Register purposes:

Callee-saved registers

- value is preserved by any function you call

- the registers we use

Callee-saved registers

- value is preserved by any function you call

- the registers we use

40

New cards

stack pointer

Points to the top of the stack

- is decremented when the stack grows

- 64 bits wide

- is decremented when the stack grows

- 64 bits wide

41

New cards

Zero Register

gives value 0 when read from

- discards value when written to

- discards value when written to

42

New cards

Program Counter

Holds the address of the currently executing instruction

- Cannot be accessed directly as a named register

- Is changed indirectly by branch and other instructions

- Is used implicitly by PC-relative load/stores

- Cannot be accessed directly as a named register

- Is changed indirectly by branch and other instructions

- Is used implicitly by PC-relative load/stores

43

New cards

branch-and-link instruction

An instruction that branches to an address, arguments are placed into x0-x7 before the call, the return value is placed in x0

- E.g, used for printf

- E.g, used for printf

44

New cards

boilerplate

.global main

main: stp x29, x30, [sp, -16]! |

mov x29, sp | ← Saves State

.

.

.

ldp x29, x30, [sp], 16 | ← Restores State

ret

main: stp x29, x30, [sp, -16]! |

mov x29, sp | ← Saves State

.

.

.

ldp x29, x30, [sp], 16 | ← Restores State

ret

45

New cards

multiplication

Uses 1 destination and 2 or 3 source registers

NO IMMEDIATES ALLOWED

mul, Wd, Wn, Wm

calculates:

Wd = Wn x Wm

NO IMMEDIATES ALLOWED

mul, Wd, Wn, Wm

calculates:

Wd = Wn x Wm

46

New cards

multiply add

madd Wd, Wn, Wm, Wa

calculates:

Wd = Wa + (Wn x Wm)

calculates:

Wd = Wa + (Wn x Wm)

47

New cards

multiply subtract

msub Wd, Wn, Wm, Wa

calculates:

wd = wa - (wn x wm)

calculates:

wd = wa - (wn x wm)

48

New cards

multiply negate

mneg Wd, Wn, Wm

calculates:

Wd = -(Wn x Wm)

calculates:

Wd = -(Wn x Wm)

49

New cards

division

NO IMMEDIATES ALLOWED

signed form: sdiv Wd, Wn, Wm = Wd = Wn / Wm

unsigned form: udiv x21, x22, x23

Used integer division

The remainder (or modulus) can be calculated using num - (quotient * denominator)

signed form: sdiv Wd, Wn, Wm = Wd = Wn / Wm

unsigned form: udiv x21, x22, x23

Used integer division

The remainder (or modulus) can be calculated using num - (quotient * denominator)

50

New cards

the four flags

Z: true if the result is 0

N: true if the result is negative

V: true if the result overflows

C: true if result generates a carry out

N: true if the result is negative

V: true if the result overflows

C: true if result generates a carry out

51

New cards

Condition Flags

may be used to store information about the result of an instruction

- Are single-bit in the CPU

- Record process state(PSTATE) information

- 0 means false, 1 means true

- Are single-bit in the CPU

- Record process state(PSTATE) information

- 0 means false, 1 means true

52

New cards

2^n

An n bit register can hold ____ bit patterns

53

New cards

Unsigned integers

Are encoded using binary numbers

- Range 0 to 2^N -1, where N is the number of bits

- Range 0 to 2^N -1, where N is the number of bits

54

New cards

Signed integers

most commonly encoded using the two's complement representation

Range: -2^(N-1) to +2^(N-1) -1

- E.g 4-bits: -8 to +7

- E.g 8-bits: -128 to +127

- E.g 16-bits: -32,768 to +32,767

All positive numbers will have a 0 in the left-most bit

And all the negative numbers will have 1subt

Range: -2^(N-1) to +2^(N-1) -1

- E.g 4-bits: -8 to +7

- E.g 8-bits: -128 to +127

- E.g 16-bits: -32,768 to +32,767

All positive numbers will have a 0 in the left-most bit

And all the negative numbers will have 1subt

55

New cards

two's complement

1. Taking the one's complement toggle all 0's to 1's, and vice versa

2. adding 1 to the result

2. adding 1 to the result

56

New cards

Hexadecimal

Prefixed by 0x

- 0, 1, 2, ..., 9, A, B, C, D, E, F

A = 10, B = 11, C = 12, D = 13, E = 14, F = 15

- 0, 1, 2, ..., 9, A, B, C, D, E, F

A = 10, B = 11, C = 12, D = 13, E = 14, F = 15

57

New cards

Octal

prefixed by 0

- 0 to 7

- May be used as a shorthand for denoting bit patterns (each digit corresponds to a 3 bit pattern)

- 0 to 7

- May be used as a shorthand for denoting bit patterns (each digit corresponds to a 3 bit pattern)

58

New cards

logical shift right

lsl xd, xn, xm

Xn: bit pattern to be shifted

Xm: shift count

- 0 is shifted into the right most bit, shifted out bits are lost

quick way to do division by a power of two

- DOES NOT WORK FOR NEGATIVE SIGNED INTEGERS, MUST USE ASR

I.e. by 2^n, where n is the shift count

Xn: bit pattern to be shifted

Xm: shift count

- 0 is shifted into the right most bit, shifted out bits are lost

quick way to do division by a power of two

- DOES NOT WORK FOR NEGATIVE SIGNED INTEGERS, MUST USE ASR

I.e. by 2^n, where n is the shift count

59

New cards

Logical Shift Left

lsl xd, xn, xm

Xn: bit pattern to be shifted

Xm: shift count

- 0 is shifted into the right most bit, shifted out bits are lost

quick way to do multiplication by a power of two

I.e. by 2^n, where n is the shift count

Xn: bit pattern to be shifted

Xm: shift count

- 0 is shifted into the right most bit, shifted out bits are lost

quick way to do multiplication by a power of two

I.e. by 2^n, where n is the shift count

60

New cards

Arithmetic Shift Right

Works like lsr (completes division by a power of 2), except sign bit is duplicated when shifting

Called sign extension

Called sign extension

61

New cards

Signed Extend Byte

Form (32 bit): sxtb, Wd, Wn

Sign-extends bit 7 in Wn to bits 8-31

Sign-extends bit 7 in Wn to bits 8-31

62

New cards

Signed Extend Halfword

Form (32 bit): sxth Wd, Wn

Sign extends bit 15 in Wn to bits 16-31

Sign extends bit 15 in Wn to bits 16-31

63

New cards

Sign Extend Word

Form (64 bit): sxtw Xn, Wn

Sign-extends bit 31 to bits 32-63

Sign-extends bit 31 to bits 32-63

64

New cards

Unsigned Extend Byte

Form (32 bit ONLY): uxtb Wd, Wn

Zero extends bits 8-31

Zero extends bits 8-31

65

New cards

Unsigned Extend Halfword

Form (32 bit): uxth Wd, Wn

Zero extends bits 16-31

Zero extends bits 16-31

66

New cards

subtraction

_____________ is done in the ALU by negating the subtrahend, and then adding

- e.g 7-5 = 7 + (-5) = 0111 + 1011 = (1) 0010, where we ignore the carry out

- e.g 7-5 = 7 + (-5) = 0111 + 1011 = (1) 0010, where we ignore the carry out

67

New cards

Z == 1

Signed number branching conditions:

eq (equal)

eq (equal)

68

New cards

Z == 0

Signed number branching conditions:

ne (not equal)

ne (not equal)

69

New cards

Z == 0 && N == V

Signed number branching conditions:

gt (greater than)

gt (greater than)

70

New cards

N == V

Signed number branching conditions:

ge (greater than or equal)

ge (greater than or equal)

71

New cards

N != V

Signed number branching conditions:

lt (less than)

lt (less than)

72

New cards

!(Z == 0 && N == V)

Signed number branching conditions:

le (less than or equal)

le (less than or equal)

73

New cards

Byte

1 byte

8 bits

char in C

8 bits

char in C

74

New cards

halfword

2 bytes

16 bits

short int in C

16 bits

short int in C

75

New cards

word

4 bytes

32 bits

int in C

32 bits

int in C

76

New cards

doubleword

8 bytes

64 bits

long int in C, void

64 bits

long int in C, void

77

New cards

Load Register

ldr X, ,addr

- loads register with 8 bytes read from RAM

- loads register with 8 bytes read from RAM

78

New cards

Load Byte

ldrb Wt, addr

- 32 bit only!

- loads 1 byte from RAM into low order part of Wt, sign extending high order bits

- 32 bit only!

- loads 1 byte from RAM into low order part of Wt, sign extending high order bits

79

New cards

Load signed byte

ldrsb Xt, addr

- Loads 1 byte from RAM into low-order part of Wt or Xt, sign-extending high-order bits

- Loads 1 byte from RAM into low-order part of Wt or Xt, sign-extending high-order bits

80

New cards

load halfword

ldrh Wt, addr

- 32 bit only!

- Loads 2 bytes from RAM into Wt, zero-extending high-order bits

- 32 bit only!

- Loads 2 bytes from RAM into Wt, zero-extending high-order bits

81

New cards

Load Signed Halfword

ldrsh Xt, addr

- Loads 2 bytes from RAM into Wt or Xt, sign extending high-order bits

- Loads 2 bytes from RAM into Wt or Xt, sign extending high-order bits

82

New cards

Load Signed Word

ldrsw Xt, addr

- Loads 4 bytes from RAM into Xt, sign-extending high-order bits

- Loads 4 bytes from RAM into Xt, sign-extending high-order bits

83

New cards

store register

str Xt, addr

- Stores doubleword (8 bytes) in Xt to RAM

- Stores doubleword (8 bytes) in Xt to RAM

84

New cards

store byte

strb Wt, addr

- 32 bit only!

- Stores low-order byte in Wt to RAM

- 32 bit only!

- Stores low-order byte in Wt to RAM

85

New cards

Store halfword

strh Wt, addr

- 32 bit only!

- Stores low-order halfword (2 bytes) in Wt to RAM

- 32 bit only!

- Stores low-order halfword (2 bytes) in Wt to RAM

86

New cards

dereferencing

square brackets are used for ____________ addresses

- e.g ldr x21, [x20], address is in x20

- e.g ldr x21, [x20], address is in x20

87

New cards

Pre-indexed addressing

address expression is calculated first

- e.g ldr x21, [x20, 10]

- address is x20 + 10

- x20 does not change

e.g ldr x21, [x20, 10]!

- address is x20 + 10

- x20 changes to x20 + 10

- e.g ldr x21, [x20, 10]

- address is x20 + 10

- x20 does not change

e.g ldr x21, [x20, 10]!

- address is x20 + 10

- x20 changes to x20 + 10

88

New cards

Post-indexed addressing

address expression calculated after

e.g ldr x21, [x20], 10

- address is x20

- x20 changes to x20 + 10

e.g ldr x21, [x20], 10

- address is x20

- x20 changes to x20 + 10

89

New cards

Descending stack

grows from higher to a lower address

90

New cards

ascending stack

grows from a lower to a higher address

91

New cards

Full Stack

the stack pointer points at the top of the stack (last pushed item)

92

New cards

empty stack

the stack pointer points to the next free space on the top of the stack

93

New cards

Stack Memory

space in RAM provided by the OS to store data for functions/procedures/routines

94

New cards

stack frame

is pushed (and created )onto the stack when the function is called

- Holds the function's parameters, local variables, and return values

- Is a descending, full stack

- contains FP and LR for the calling routine (restored when the current routine returns)

is popped (and destroyed) when the function returns

- Holds the function's parameters, local variables, and return values

- Is a descending, full stack

- contains FP and LR for the calling routine (restored when the current routine returns)

is popped (and destroyed) when the function returns

95

New cards

high memory

the stack uses ___________

grows backwards (towards 0)

grows backwards (towards 0)

96

New cards

low memory

programs are loaded into _______________

- just above the space reserved for the OS

- just above the space reserved for the OS

97

New cards

heap

is used for dynamically allocated memory in a program

98

New cards

subtracting

A program can allocate stack memory by _____________ the number of bytes needed from SP

- e.g sub sp, sp, 16

- e.g sub sp, sp, 16

99

New cards

quadword aligned

the stack must be __________________________

- the address in SP must be evenly divisible by 16

- e.g to allocate 20 bytes

add sp, sp, -20 & -16

- the address in SP must be evenly divisible by 16

- e.g to allocate 20 bytes

add sp, sp, -20 & -16

100

New cards

frame pointer

register x29

- Is used to point to local variables in a stack frame

- Is stable, once set at the beginning of a function

- in contrast, SP is unstable - Allowed to change as the function executes

- Is used to point to local variables in a stack frame

- Is stable, once set at the beginning of a function

- in contrast, SP is unstable - Allowed to change as the function executes