systems architecture

1/27

Earn XP

Description and Tags

+ fetch execute cycle + harvard architecture

Name | Mastery | Learn | Test | Matching | Spaced | Call with Kai |

|---|

No analytics yet

Send a link to your students to track their progress

28 Terms

describe computer architecture

von nuemann architecture is a design model for computers where all computers have 1 memory which is shared between programs + data (represented in binary)

what are the main components of von nueman architecture

memory

buses

processor (registers)

what are the three main components of any computer system & define them

arithmetic logic unit (processes data)

control unit (supervises & synchronises running of processor)

main memory/ immediate access store (ROM & RAM)

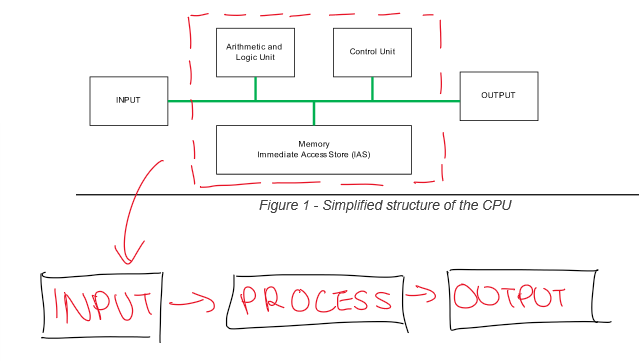

describe the simple structure of the CPU in a diagram

what are peripherals and how are they connected to computer?

Devices that connect to a computer to add functionality, such as input/output devices like keyboards, mice, printers, and storage devices.

theyre connected to computer via contollers (hardware) e.g.:

keyboard controllers

mouse controllers

disk controllers

monitor controllers

how is the computer’s memory structured?

divided into set of fixed length blocks which contain data or instructions stored as binary.

each block has a unique address (memory address)

what is a ‘word’ in relation to memory

specific group of binary digits

if memory word size = 8 bits, it means each memory location can store an 8 bit binary number (byte)

its fixed at manufacture

factors affecting processor speed:

word size (higher word size = more data pulled on during a clock cycle = faster processor speed)

data bus (bigger bus = more data pulled on during a clock cycle = faster processor speed)

define the term bus

the communication lines (parallel wires) which join parts of the processor together

what are the 3 main buses & what is their purpose

data bus (carry data around processor)

address bus (points to next memory location to be accessed)

control bus (states action to be executed)

how is the address bus used by the computer

when CPU wants to access memory location, memory address is ‘put’ onto bus and the bits travel in parallel - the width of the bus determines the number of memory addresses that can be accessed.

its unidirectional (one way)

typically 32 lines wide

how is the number of memory locations accessed by address bus calculated?

2x lines wide

e.g.

address bus = 3 lines wide

23 = 8

so 8 memory locations can be accessed by address bus of 3 line width

if I need to access 64 memory locations, how many lines wide does my address bus have to be?

2x = 64

Log2(64) = 6

answer = 6

how is the data bus used by the computer

transports data in AND out of the processor so its bi-directional (two way)

typically 32 lines wide

how is the control bus used by the computer

sends control signals to time/ synchronise operations in both directions (bi-directional)

typically 8 lines wide

examples of control signals sent along control bus

memory read/ write

request signals

handshake signals

clock signal

reset signal

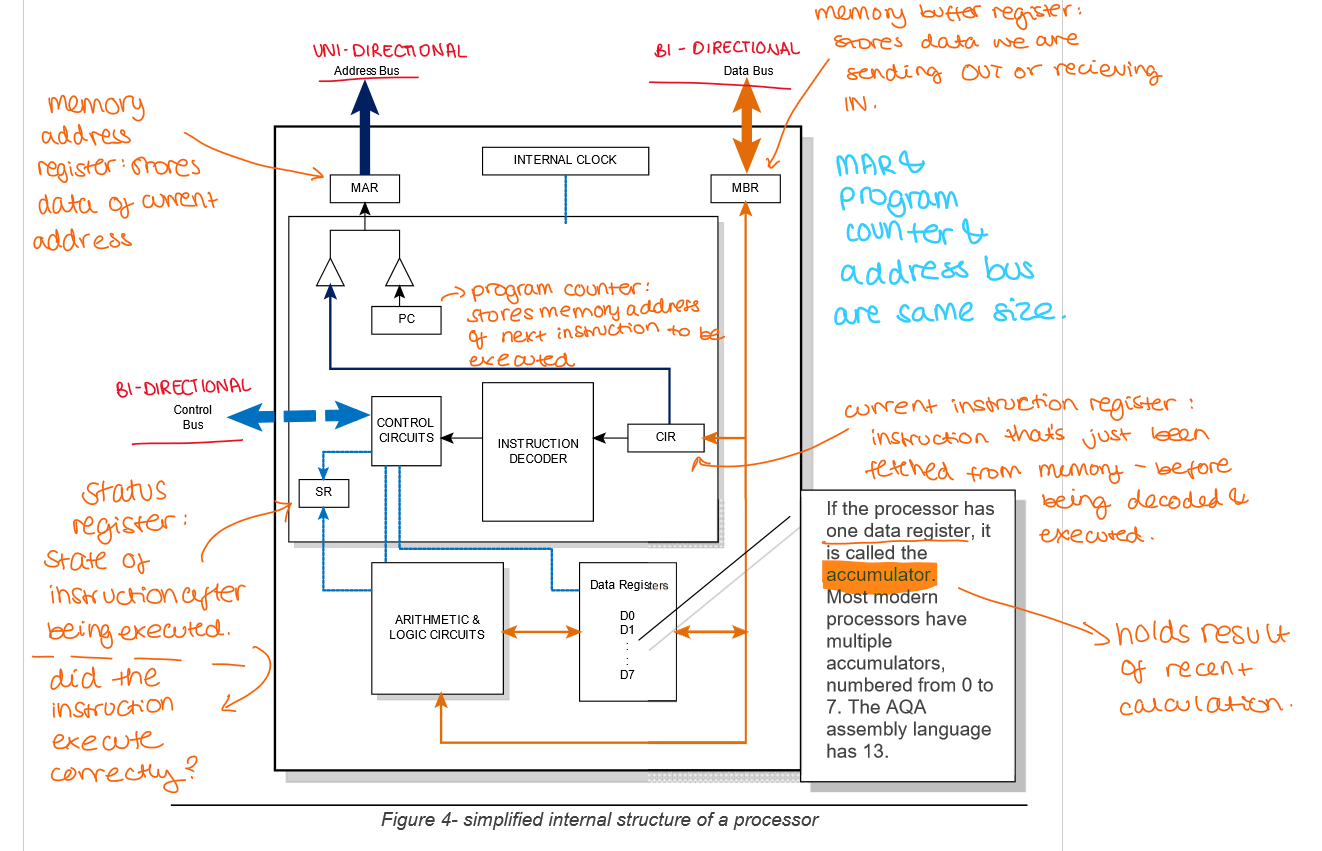

what are the key parts of the processor & their functions?

program control unit (fetches, decodes and executes instructions)

arithmetic & logic unit (performs all arithmetic/ Boolean logic)

registers (very fast memory locations)

internal clock (synchronises system)

internal buses (link components together & transfer data)

diagram of the processor

what is it meant by a general purpose register

registers which are available to store temporary data during arithmetic operations

(if processor only uses one register- it is the accumulator as it stores result of calculation)

e.g. assembly language: LDR R0, #10

state all the dedicated registers used by the program counter

stack pointer (points to stack holding return address during procedure/ function/ interrupt)

program counter (holds memory address of NEXT instruction)

status register (holds condition codes (e.g. +ve -ve) to indicate outcome of operations)

accumulator (holds result of current calculation)

current instruction register (holds copy of current instruction to be executed)

memory address register (holds memory address of current instruction)

memory buffer register (holds data of current instruction)

+1 register (increments program counter)

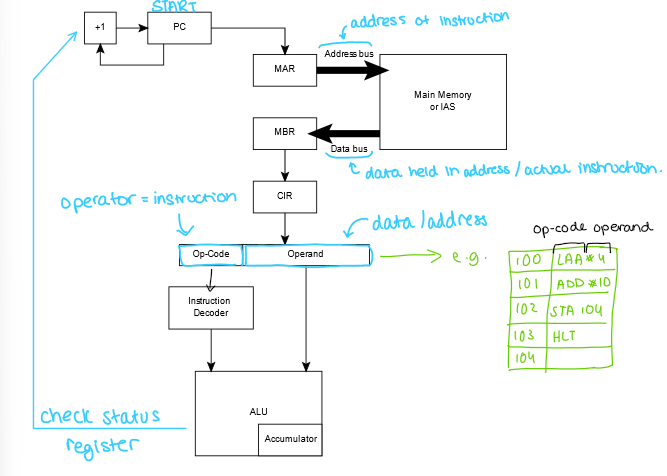

describe the fetch execute cycle:

FETCH

contents of PC copied to MAR & PC is incremented by 1

control signal sent to read contents of current instruction

current instruction’s address copied from PC to MAR via address bus

current instruction’s data copied from main memory to MBR via data bus

a copy of this is stored in CIR

DECODE

instruction is divided into op-code (instruction) and operand (data/ address)

this is translated into commands the hardware can interpret (assembly language)

EXECUTE

op-code is passed into instruction decoder whilst operands are used during execution

any logical operations are calculated by ALU and the result is stored in ACC

status register is checked

op-code

the instruction

e.g. LDR, ADD, HLT

operand

data/ address

e.g. #10, 104,101, #4

what is an interrupt

signal sent to processor requesting its attention

why are interrupts necessary?

responsiveness (allow processor to handle urgent tasks promptly without having to wait for current instruction to finish executing)

resource management (allow processor to allocate memory, processors & I/O devices among competing processes)

event handling (enable system to respond to external events in real-time)

how do interrupts work?

processor suspends current program execution

contents of all registers are preserved on stack (if this isn’t done, system may loose critical info about interrupted program so it ensures program is resumed correctly)

control is vectored to interrupt service routine (ISR)

after ISR completes its task, processor ‘pops' off’ preserved registers from stack to resume executing original task

describe Harvard Architecture

physically separates storage & signal pathways for instructions and data so that there is:

one memory for instruction

one memory for data itself

its used for small embedded computers and signal processing

evaluate harvard architecture

+able to read instruction and perform data memory access simultaneously at fast speed

+each memory can use different word sizes

+better audio and video processing products

-production of computer with 2 sets of buses = expensive