sequential circuits

1/33

There's no tags or description

Looks like no tags are added yet.

Name | Mastery | Learn | Test | Matching | Spaced | Call with Kai |

|---|

No analytics yet

Send a link to your students to track their progress

34 Terms

what does the output of sequential circuits depend on?

outputs depend on past sequences of inputs too (not just present inputs like combinational)

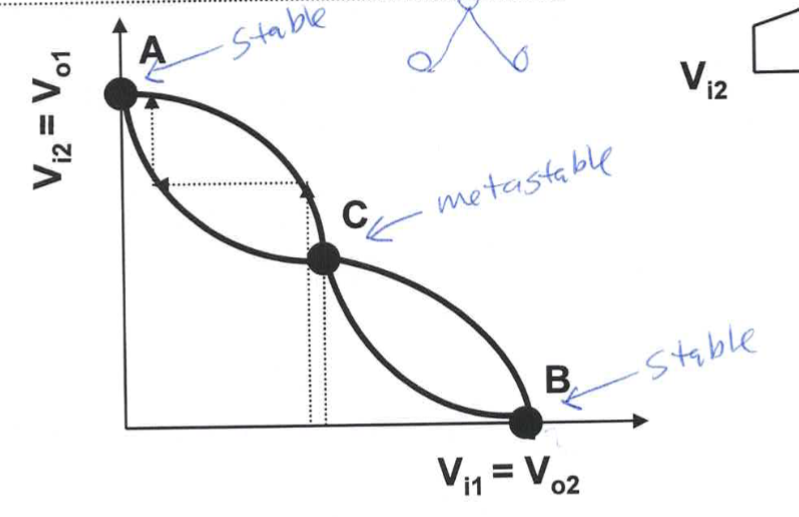

why are A and C stable?

“ball on the mountain”

Little disturbance at A and C = will go back

but if you push the ball when it is at metastable: it will roll

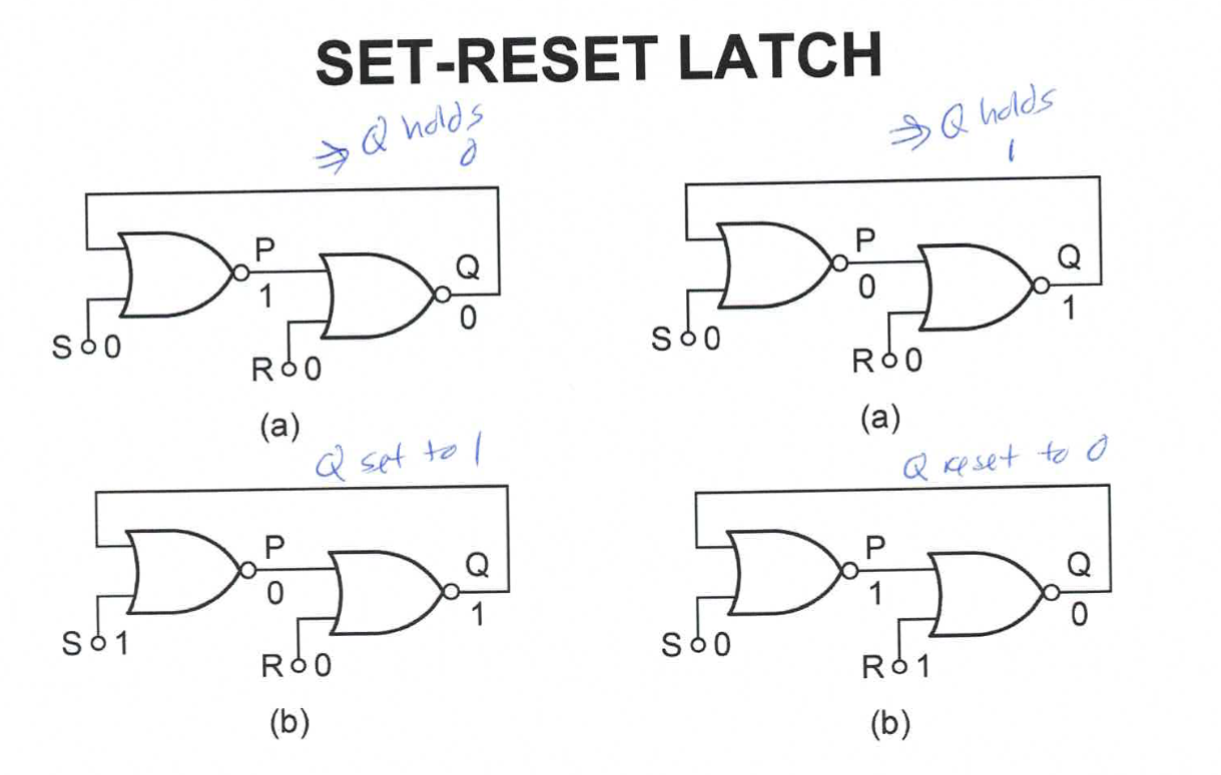

set reset latches

a way to change states using nor gates

what is the race problem in SR Latches

when SR = 11 changes to SR = 00

resulting gate depends on which gate is faster

another problem with SR latches

glitches: output could change during transition stage and reset to 0

solution: clocked sr latch

gated d latch

sr latch + clock

probelm with d lathces

level sensitive latch: output Q is sensitive to D while the clock is 1 (high)

harder synchronization for d latches because it can travel thru multiple latches

differences of latches vs flipflops

Latches: Level sensitive

Flip Flops: edge triggered, built using latches

D flip flops

stored on clock edge

master slave

when clock is 0

master enabled, loads D, appears at P

Slave is disabled

when clock is 1

master disabled, P stays the same , slave latch enabled, loads P, appears at Q

what happens to the D value when the clock changes from 0 to 1

gets stored into slave

what does D flip flops solve

the problem of not knowing how many latches signal travels when C = 1

how? all four flip flops are loaded simultaneously during rising edge, won’t pay attention to their inputs until the next edge

what are some problems with gating the clock

if the enable change at the wrong time, this may create an extra clock edge

this cause loss of synchronization

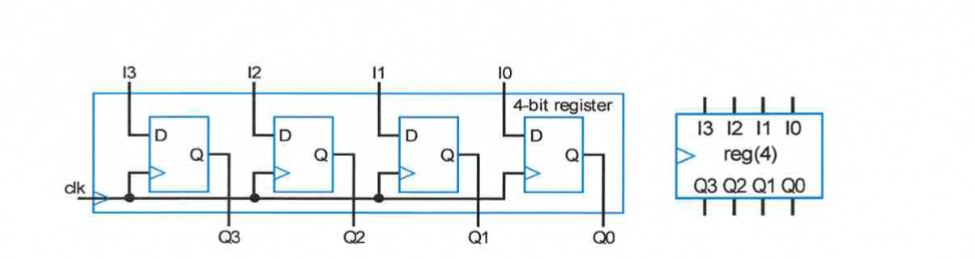

Basic register

multiple flip flops sharing clock signals

shift register

if a feed back is added, cyclic shift register forms

johnson counter

shift register where there’s a feedback

cycle length = 2 * (number of flipflops)

moore machine

outputs associated with state

mealy

output associated with input and states

complete specified state graphs

OR of all outgoing edges = 1

AND of any pair of outgoing edges = 0

how bits does an N-bit register store? what is N

n bits (the width)

how many times is the basic register loaded

every cycle

how to design a register

determine the mux size

create the mux table

connect mux inputs

map control line

blocking

uses =

complete the assignment before moving onto the next instruction

combinational

nonblocking

<=

runs the instructions simultaneously

sequential (flipflops, registers)

parameters

used to specify constant values for a module

allows parameter values to be specified when module instantiated

paramter constant_name = constant value;

localparam

similar to paramterm but cannot be changed when module instantiated

used to define constants that should not be changed

localparam constant_name = constant value