TI-WS22

1/19

Earn XP

Description and Tags

Name | Mastery | Learn | Test | Matching | Spaced | Call with Kai |

|---|

No analytics yet

Send a link to your students to track their progress

20 Terms

Wie ist die elektrische Stromstärke definiert? (I: Stromstärke, U: Spannung, t: Zeit, Q: Ladung)

A: I=tU

B: I=dtdQ

C: I=Q⋅t

B: I=dtdQ

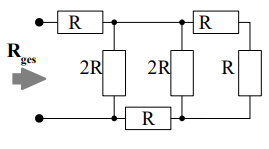

Wie groß ist der Gesamtwiderstand R<em>ges des folgenden Netzwerkes?

A: R</em>ges=2R

B: R<em>ges=3R

C: R</em>ges=3R/2

A: Rges=2R

Worauf beruht der 2. Kirchhoffsche Satz (Maschensatz)?

A: Spannungsteilerregel

B: Ladungserhaltungssatz

C: Energieerhaltungssatz

C: Energieerhaltungssatz

Welche Aussage zu einer idealen Spannungsquelle ist richtig?

A: Eine ideale Spannungsquelle darf kurzgeschlossen werden

B: Eine ideale Spannungsquelle erzeugt eine vom Strom unabhängige Spannung

C: Eine ideale Spannungsquelle erzeugt unabhängig von ihrer Belastung einen konstanten Strom

B: Eine ideale Spannungsquelle erzeugt eine vom Strom unabhängige Spannung

Warum werden in der Digitaltechnik komplementäre Transistoren (CMOS) eingesetzt?

A: Mit komplementären Transistoren können verlustarme Schaltungen realisiert werden

B: Komplementäre Transistoren sind erforderlich, um binäre Rechenoperationen darzustellen

C: Komplementäre Transistoren sind resistenter gegen elektrostatische Aufladungen

A: Mit komplementären Transistoren können verlustarme Schaltungen realisiert werden

Welche Schaltung lässt sich prinzipiell NICHT mit einem Schaltnetz realisieren?

A: Addierer

B: Zähler

C: Komparator

B: Zähler

Welche Aussage zu einer logischen Funktion f(a,b,c) in vollkonjunktiver Normalform ist falsch?

A: Die Funktion enthält maximal 8 unter-schiedliche Maxterme

B: Die Funktion lässt sich stets in eine disjunktive Normalform überführen

C: Die Funktion kann nicht minimiert werden

C: Die Funktion kann nicht minimiert werden

Welche Gleichung ist als „De Morgansches Theorem“ bekannt?

A: (a⋅b)=aˉ+bˉ

B: a+(a⋅b)=a

C: c+cˉ⋅b=c+b

A: (a⋅b)=aˉ+bˉ

Wird zur Darstellung natürlicher Zahlen der Binär-Code mit einer Wortbreite von n Bit verwendet, so gilt für das Umschalten zwischen benachbarten Werten:

A: Es müssen bis zu n Bits gleichzeitig geändert werden

B: Es müssen bis zu n/2 Bits gleichzeitig geändert werden

C: Es braucht immer nur ein einziges Bit geändert zu werden

A: Es müssen bis zu n Bits gleichzeitig geändert werden

Welche Aussage zur Codierung alphanumerischer Zeichen ist falsch?

A: Der ASCII-Code umfasst 128 Zeichen, weitere 128 sprachspezifische Zeichen sind in "Codepages" definiert

B: Der ASCII-Code enthält neben Buchstaben und Zahlen auch Steuerzeichen

C: Die "ASCII-Tabelle" ist in heutigen Rechnergenerationen unbrauchbar, da diese vom "Unicode" abgelöst wurde

C: Die "ASCII-Tabelle" ist in heutigen Rechnergenerationen unbrauchbar, da diese vom "Unicode" abgelöst wurde

Welche Eigenschaft eines Prozessors wird mit „Big Endian“ bzw. „Little Endian“ charakterisiert?

A: Die Reihenfolge, in der die Bytes einer Ganzzahl im Speicher organisiert sind

B: Die größte positive bzw. kleinste negative Zahl

C: Segmentgröße bei der dynamischen Speicherreservierung

A: Die Reihenfolge, in der die Bytes einer Ganzzahl im Speicher organisiert sind

Welche Aussage zu einer „direkten Adressierung“ ist richtig?

A: Die Adresse der Speicherstelle ist bereits zur Compilezeit bekannt

B: Die Adresse ergibt sich direkt aus dem Inhalt des Program-Counters

C: Die Adresse des Operanden ist fest vorgegeben (z.B. Stack-Operationen)

A: Die Adresse der Speicherstelle ist bereits zur Compilezeit bekannt

Ein “atomarer Befehl” in Maschinensprache wird …

A: … immer als erster Befehl in Interrupt-Routinen ausgeführt

B: … immer nur nach einem Reset ausgeführt

C: … vor jeglicher Programmverzweigung zuerst zu Ende geführt

C: … vor jeglicher Programmverzweigung zuerst zu Ende geführt

Für welche Software-Struktur ist ein „Stack“ erforderlich?

A: Bedingte Verzweigung mit if-Anweisung

B: Programmschleife mit for-Anweisung

C: Funktionsaufruf

C: Funktionsaufruf

Zur Optimierung von Datendurchsatz und Kosten von Rechnersystemen …

A: … verwendet man eine Speicher-Hierarchie

B: … verwendet man eine von-Neumann-Architektur

C: … verwendet man den Polling-Controller

A: … verwendet man eine Speicher-Hierarchie

Die Abkürzung EEPROM steht für:

A: Endlessly Erasable Programmable Read Only Memory

B: Erroneously Erasable Programmable Read Once Memory

C: Electrical Erasable Programmable Read Only Memory

C: Electrical Erasable Programmable Read Only Memory

Die Zentraleinheit eines Rechnersystems besteht laut Vorlesung aus …

A: … Prozessor, Benutzerkonsole, Hauptspeicher, PCI-Bus

B: … Steuereinheit, Verarbeitungseinheit, Speichereinheit, peripheren Interfaces

C: … Steuereinheit, Hauptspeicher, Massenspeicher, Netzwerkanschluss

B: … Steuereinheit, Verarbeitungseinheit, Speichereinheit, peripheren Interfaces

Welche Aussage zum Interrupt-Konzept ist richtig?

A: Das Interrupt-Konzept ist ungeeignet bei nötiger Sofortreaktion

B: Bei einem Ereignis wird eine spezielle Service-Routine aktiviert

C: Das Interrupt-Konzept berücksichtigt nur prozessorinterne Ereignisse

B: Bei einem Ereignis wird eine spezielle Service-Routine aktiviert

Welche Merkmale sind typisch für eine RISC-Prozessorarchitektur?

A: Pipeline-Struktur, wenige/orthogonale Befehle, wenige Adressierungsarten

B: vollständiger Befehlssatz, von-Neumann-Architektur, viele Adressierungsarten

C: umfangreicher Befehlssatz, Pipeline-Struktur, gut geeignet für Assembler

A: Pipeline-Struktur, wenige/orthogonale Befehle, wenige Adressierungsarten

Die „Instruction Set Architecture“ eines Prozessors …

A: … definiert die in einer Hochsprache verwendbaren Befehle

B: … beinhaltet Verknüpfungs-, Verzweigungs- und Transferoperationen

C: … definiert den vollständigen Befehlssatz eines Prozessors

C: … definiert den vollständigen Befehlssatz eines Prozessors