SYSC3320 - UART, I2C, SPI

1/9

There's no tags or description

Looks like no tags are added yet.

Name | Mastery | Learn | Test | Matching | Spaced | Call with Kai |

|---|

No analytics yet

Send a link to your students to track their progress

10 Terms

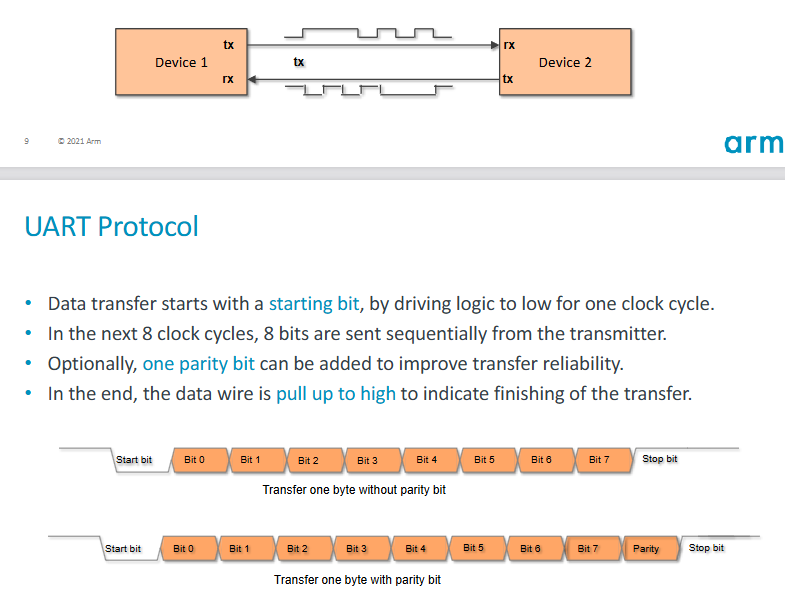

UART basics

serial communication

asynchrnous

tx and rx wires

data sent bit by bit

Start bit (low for one clock cycle) followed by 8 bits (8 bits) + parity bit

Stop bit is high for one cycle

Send text in ascii

Serial communciation vs parallel

1 bit at time

Reliable (less clock skews across differnet wires and crosstalk)

Higher clock rate

Low cost and weight

Synchronous transmissions

common clock shared by sender and receiver

efficeint transmission since only one wire for data transfer

More costly since an extra clock wire is needed

Asyhcnrnous tranmission

no clock signal sent

both must agree on a rate in advance

speacial bits sent to synchrnoize transmission

Simplex

Data transmitted only in one direction

Full duplex

Both direction tranmssion (UART and SPI)

Half duplex

Data can be transmitted in one direction at a time (I2C and CAN)

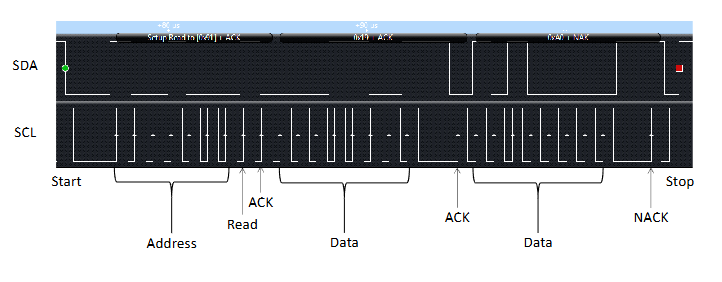

I2C overview

SDA and SCL lines that are normally pulled high

multiple devices share a serial bus

subordinates respond when addressed

Devices have 7 bit address

Sequence:

Generate start bit (low) then address + receive/send signal

Slave checks address. Slave responds with ack if match otherwise nothing.

Master receives or sends data depding on send/receive signal. If master is seniding the data, then the slave will ACK after each byte.

Master sends stop bit (high)

I2C code

LookupConfig

CfgInitialize(XIicPs_Config, Config, Config->BaseAddress);

XIicPs_SetClk(&IicInstance, IIC_SCLK_RATE);

// Send data

u8 SendBuffe3r[TEST_BUFFER_SIZE];

u8 RecvBuffer[TEST_BUFFER_SIZE];

u8 SimulatedSlaveEcho[TEST_BUFFER_SIZE]; // to simulate slave response

for (int i = 0; i < TESTBUFFERSIZE; i++) {

sendbuffer[i] = i + 1;

RecvBuffer[i] = 0;

SimulatedSlaveEcho[i] = SendBuffer[i]; //pretend slave received

print everyhting if you like

}

// Master send

Status = XIicPs_MasterSendPolled(&IicInstance, SendBuffer, TEST_BUFFER_SIZE, IIC_SLAVE_ADDR);

// wait until not busy

while (XIicPs_BusIsBusy(&IicInstance));

// Simulate receive

memcpy(RecvBuffer, SimulatedSlaveEcho, TEST_BUFFER_SIZE);

// print sent data

// print received data

// check that each byte matches otherwise return XST_FAILURE;SPI code

lookup config

cfgintialize

XSpi_SelfTest // self test

// Setup interrupt system

SetupInterruptSystem

// Register interrupt handler for SPI

XSpi_SetStatusHandler(SpiInstancePtr, SpiInstancePtr, (XSpi_StatusHandler)SpiIntrHandler);

XSpi_SetOptions(SpiInstancePtr, XSP_MASTER_OPTION | XSP_MANUAL_SSELECT_OPTION)

// Manually select slave

XSpi_SetSlaveSelect(SPIInstancePrt, 0x01);

XSpi_Start(SPiInstancPtr);

Setup write and read buffers

TransferInProgress = TRUE; // volatile + static var

XSpi_Transfer(SpiInstancePtr, WriteBuffer, ReadBuffer, BUFFER_SIZE);

while (TransferInProgress); // Updated by interrupt handler

// Check WriteBuffer against ReadBuffer

void SpiIntrHandler(void *CallbackRef, u32 StatusEvent, unsigned int ByteCount) {

if statusevent != XST_SPI_TRANSFER_DONE: errorcount++

TransferInProgress = FALSE;

}